|

vt52-fpga

1.0.0 Initial

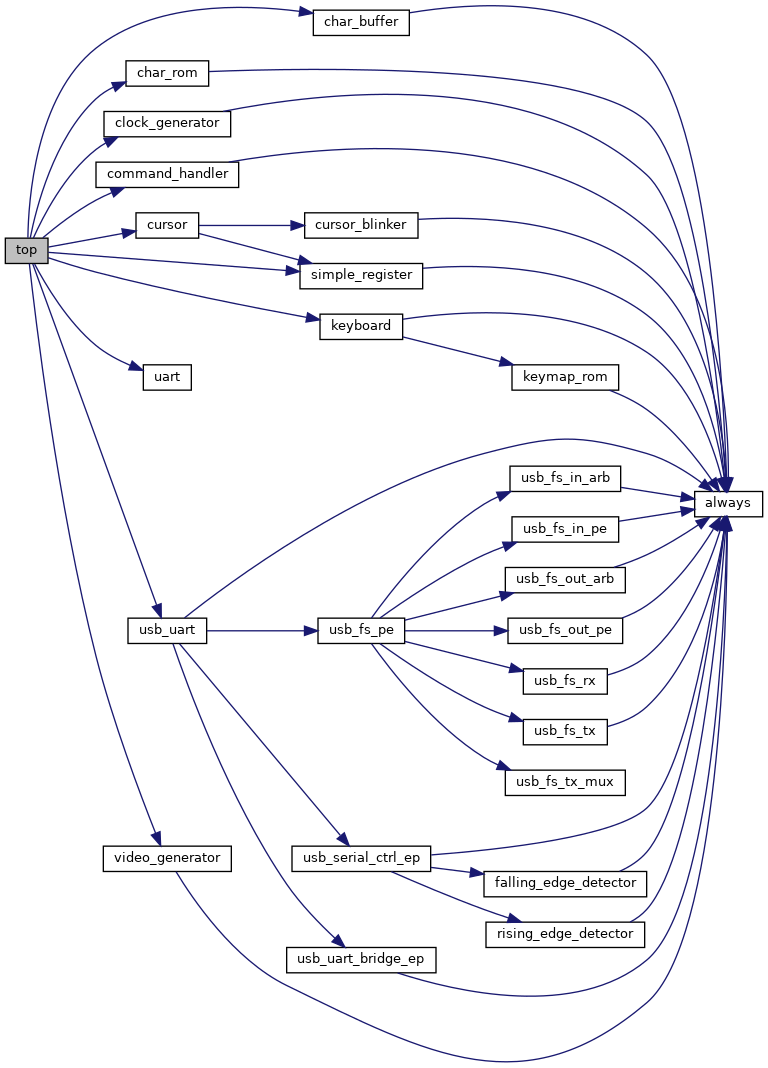

vt52-fpga is a serial terminal implemented on a FPGA

|

|

vt52-fpga

1.0.0 Initial

vt52-fpga is a serial terminal implemented on a FPGA

|

Functions | |

| template<parameter BUF_SIZE = 1920, parameter ADDR_BITS = 11> | |

| module | char_buffer (input wire clk, input wire< 7:0 > din, input wire< ADDR_BITS-1:0 > waddr, input wire wen, input wire< ADDR_BITS-1:0 > raddr, output reg< 7:0 > dout, input wire graphic_mode) |

| Char Buffer RAM (1920x8) (24 lines of 80 characters) More... | |

| module | char_rom (input clk, input[11:0] addr, output[8] dout_) |

| Character Font ROM (4kx8) This could be a RAM to allow font modifications, but not for now latin-1 subset of Terminus Font 8x16 (http://terminus-font.sourceforge.net) Terminus Font is licensed under the SIL Open Font License, Version 1.1. More... | |

| module | clock_generator (input clk, output clk_usb, output reset_usb, output clk_vga, output reset_vga) |

| template<parameter ROWS = 24, parameter COLS = 80, parameter LAST_ROW = (ROWS-1) * COLS, parameter ONE_PAST_LAST_ROW = ROWS * COLS, parameter ROW_BITS = 5, parameter COL_BITS = 7, parameter ADDR_BITS = 11> | |

| module | command_handler (input clk, input reset, input[8] data, input valid, output ready, output[ADDR_BITS-1:0] new_first_char, output new_first_char_wen, output[8] new_char, output[ADDR_BITS-1:0] new_char_address, output new_char_wen, output[COL_BITS-1:0] new_cursor_x, output[ROW_BITS-1:0] new_cursor_y, output new_cursor_wen, output graphic_mode) |

| template<parameter ROW_BITS = 5, parameter COL_BITS = 7> | |

| module | cursor (input clk, input reset, input tick, output wire< COL_BITS-1:0 > x, output wire< ROW_BITS-1:0 > y, output wire blink_on, input[COL_BITS-1:0] new_x, input[ROW_BITS-1:0] new_y, input wen) |

| Cursor (position and blinking) More... | |

| module | cursor_blinker (input clk, input reset, input tick, input reset_count, output wire blink_on) |

| Cursor blinker (uses vblank as tick, blinks about once a second) More... | |

| module | keyboard (input clk, input reset, input ps2_data, input ps2_clk, output reg< 7:0 > data, output reg valid, input ready) |

| module | keymap_rom (input clk, input[10:0] addr, output[8] dout_) |

| Keymap ROM (2KB, maps keycodes to ASCII chars) This could be a RAM to allow keymap modifications, but not for now There's 8 planes for each keycode (controlled by the highest three bits) MSB is for long keycode vs short keycode, the the next two bits: 00: no shift or caps lock 01: just shift 10: just caps lock 11: caps lock & shift. More... | |

| template<parameter SIZE = 8> | |

| module | simple_register (input wire clk, input wire reset, input wire< SIZE-1:0 > idata, input wire wen, output reg< SIZE-1:0 > odata) |

| Basic register with synchronous set & reset. More... | |

| module | clock_pll48 (input clk_in, output clk_out, output clk_reset, output clk_tick) |

| module | rising_edge_detector (input clk, input in, output out) |

| module | falling_edge_detector (input clk, input in, output out) |

| template<parameter INPUT_WIDTH = 8, parameter OUTPUT_WIDTH = 1> | |

| module | width_adapter (input clk, input reset, input data_in_put, output data_in_free, input[INPUT_WIDTH-1:0] data_in, output data_out_put, input data_out_free, output[OUTPUT_WIDTH-1:0] data_out) |

| template<parameter NUM_IN_EPS = 1> | |

| module | usb_fs_in_arb (input[NUM_IN_EPS-1:0] in_ep_req, output reg< NUM_IN_EPS-1:0 > in_ep_grant, input[(NUM_IN_EPS *8) -1:0] in_ep_data, output reg< 7:0 > arb_in_ep_data) |

| template<parameter NUM_IN_EPS = 11, parameter MAX_IN_PACKET_SIZE = 32> | |

| module | usb_fs_in_pe (input clk, input reset, input[NUM_IN_EPS-1:0] reset_ep, input[7] dev_addr, output reg< NUM_IN_EPS-1:0 > in_ep_data_free=0, input[NUM_IN_EPS-1:0] in_ep_data_put, input[8] in_ep_data, input[NUM_IN_EPS-1:0] in_ep_data_done, input[NUM_IN_EPS-1:0] in_ep_stall, output reg< NUM_IN_EPS-1:0 > in_ep_acked=0, input rx_pkt_start, input rx_pkt_end, input rx_pkt_valid, input[4] rx_pid, input[7] rx_addr, input[4] rx_endp, input[10:0] rx_frame_num, output reg tx_pkt_start=0, input tx_pkt_end, output reg< 3:0 > tx_pid=0, output tx_data_avail, input tx_data_get, output reg< 7:0 > tx_data, output[8] debug) |

| template<parameter NUM_OUT_EPS = 1> | |

| module | usb_fs_out_arb (input[NUM_OUT_EPS-1:0] out_ep_req, output reg< NUM_OUT_EPS-1:0 > out_ep_grant) |

| template<parameter NUM_OUT_EPS = 1, parameter MAX_OUT_PACKET_SIZE = 32> | |

| module | usb_fs_out_pe (input clk, input reset, input[NUM_OUT_EPS-1:0] reset_ep, input[7] dev_addr, output[NUM_OUT_EPS-1:0] out_ep_data_avail, output reg< NUM_OUT_EPS-1:0 > out_ep_setup=0, input[NUM_OUT_EPS-1:0] out_ep_data_get, output reg< 7:0 > out_ep_data, input[NUM_OUT_EPS-1:0] out_ep_stall, output reg< NUM_OUT_EPS-1:0 > out_ep_acked=0, input[NUM_OUT_EPS-1:0] out_ep_grant, input rx_pkt_start, input rx_pkt_end, input rx_pkt_valid, input[4] rx_pid, input[7] rx_addr, input[4] rx_endp, input[10:0] rx_frame_num, input rx_data_put, input[8] rx_data, output reg tx_pkt_start=0, input tx_pkt_end, output reg< 3:0 > tx_pid=0) |

| template<parameter NUM_OUT_EPS = 1, parameter NUM_IN_EPS = 1> | |

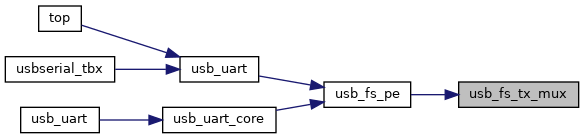

| module | usb_fs_pe (input clk, input[7] dev_addr, input reset, input[NUM_OUT_EPS-1:0] out_ep_req, output[NUM_OUT_EPS-1:0] out_ep_grant, output[NUM_OUT_EPS-1:0] out_ep_data_avail, output[NUM_OUT_EPS-1:0] out_ep_setup, input[NUM_OUT_EPS-1:0] out_ep_data_get, output[8] out_ep_data, input[NUM_OUT_EPS-1:0] out_ep_stall, output[NUM_OUT_EPS-1:0] out_ep_acked, input[NUM_IN_EPS-1:0] in_ep_req, output[NUM_IN_EPS-1:0] in_ep_grant, output[NUM_IN_EPS-1:0] in_ep_data_free, input[NUM_IN_EPS-1:0] in_ep_data_put, input[(NUM_IN_EPS *8) -1:0] in_ep_data, input[NUM_IN_EPS-1:0] in_ep_data_done, input[NUM_IN_EPS-1:0] in_ep_stall, output[NUM_IN_EPS-1:0] in_ep_acked, output sof_valid, output[10:0] frame_index, output usb_p_tx, output usb_n_tx, input usb_p_rx, input usb_n_rx, output usb_tx_en, output[8] debug) |

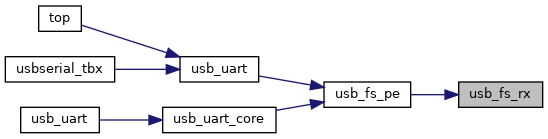

| module | usb_fs_rx (input clk_48mhz, input reset, input dp, input dn, output bit_strobe, output pkt_start, output pkt_end, output[4] pid, output reg< 6:0 > addr=0, output reg< 3:0 > endp=0, output reg< 10:0 > frame_num=0, output rx_data_put, output[8] rx_data, output valid_packet) |

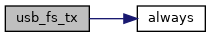

| module | usb_fs_tx (input clk_48mhz, input reset, input bit_strobe, output reg oe=0, output reg dp=0, output reg dn=0, input pkt_start, output pkt_end, input[4] pid, input tx_data_avail, output reg tx_data_get=0, input[8] tx_data) |

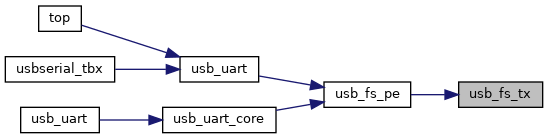

| module | usb_fs_tx_mux (input in_tx_pkt_start, input[4] in_tx_pid, input out_tx_pkt_start, input[4] out_tx_pid, output tx_pkt_start, output[4] tx_pid) |

| module | usb_reset_det (input clk, output reset, input usb_p_rx, input usb_n_rx) |

| template<parameter MAX_IN_PACKET_SIZE = 32, parameter MAX_OUT_PACKET_SIZE = 32> | |

| module | usb_serial_ctrl_ep (input clk, input reset, output[7] dev_addr, output out_ep_req, input out_ep_grant, input out_ep_data_avail, input out_ep_setup, output out_ep_data_get, input[8] out_ep_data, output out_ep_stall, input out_ep_acked, output in_ep_req, input in_ep_grant, input in_ep_data_free, output in_ep_data_put, output reg< 7:0 > in_ep_data=0, output in_ep_data_done, output reg in_ep_stall, input in_ep_acked) |

| module | usb_uart (input clk_48mhz, input reset, output usb_p_tx, output usb_n_tx, input usb_p_rx, input usb_n_rx, output usb_tx_en, input[8] uart_in_data, input uart_in_valid, output uart_in_ready, output[8] uart_out_data, output uart_out_valid, input uart_out_ready, output[11:0] debug) |

| module | usb_uart_bridge_ep (input clk, input reset, output out_ep_req, input out_ep_grant, input out_ep_data_avail, input out_ep_setup, output out_ep_data_get, input[8] out_ep_data, output out_ep_stall, input out_ep_acked, output in_ep_req, input in_ep_grant, input in_ep_data_free, output in_ep_data_put, output[8] in_ep_data, output in_ep_data_done, output in_ep_stall, input in_ep_acked, input[8] uart_in_data, input uart_in_valid, output uart_in_ready, output[8] uart_out_data, output uart_out_valid, input uart_out_ready, output[4] debug) |

| module | usb_uart_core (input clk_48mhz, input reset, output usb_p_tx, output usb_n_tx, input usb_p_rx, input usb_n_rx, output usb_tx_en, input[8] uart_in_data, input uart_in_valid, output uart_in_ready, output[8] uart_out_data, output uart_out_valid, input uart_out_ready, output[11:0] debug) |

| template<parameter PipeSpec = PS_d8> | |

| module | usb_uart (input clk_48mhz, input reset, inout pin_usb_p, inout pin_usb_n, inout[P_m(PipeSpec):0] pipe_in, inout[P_m(PipeSpec):0] pipe_out, output[11:0] debug) |

| module | usb_uart_np (input clk_48mhz, input reset, inout pin_usb_p, inout pin_usb_n, input[8] uart_in_data, input uart_in_valid, output uart_in_ready, output[8] uart_out_data, output uart_out_valid, input uart_out_ready, output[11:0] debug) |

| module | usb_uart (input clk_48mhz, input reset, inout pin_usb_p, inout pin_usb_n, input[8] uart_in_data, input uart_in_valid, output uart_in_ready, output[8] uart_out_data, output uart_out_valid, input uart_out_ready, output[11:0] debug) |

| module | usb_uart (input clk_48mhz, input reset, inout pin_usb_p, inout pin_usb_n, input[8] uart_in_data, input uart_in_valid, output uart_in_ready, output[8] uart_out_data, output uart_out_valid, input uart_out_ready, output det_reset, output[11:0] debug) |

| module | usbserial_tbx (input pin_clk, inout pin_usb_p, inout pin_usb_n, output pin_pu, input pin_button, output led_red, output led_green, output led_blue, output pin_led) |

| template<parameter ROWS = 24, parameter COLS = 80, parameter ROW_BITS = 5, parameter COL_BITS = 7, parameter ADDR_BITS = 11> | |

| module | video_generator (input clk, input reset, output reg hsync, output reg vsync, output reg video, output reg hblank, output reg vblank, input[COL_BITS-1:0] cursor_x, input[ROW_BITS-1:0] cursor_y, input cursor_blink_on, input[ADDR_BITS-1:0] first_char, output wire< ADDR_BITS-1:0 > char_buffer_address, input[8] char_buffer_data, output wire< 11:0 > char_rom_address, input[8] char_rom_data, input graphic_mode_state) |

| 80x24 char generator (8x16 char size) & sync generator More... | |

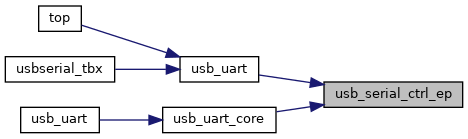

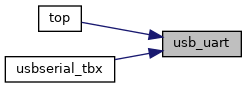

| module | top (input pin_clk, output wire vga_clk, output wire vga_blank, output wire hsync, output wire vsync, output wire< 7:0 > vga_r, output wire< 7:0 > vga_g, output wire< 7:0 > vga_b, output wire pin_led, input ps2_data, input ps2_clk, inout pin_usb_p, inout pin_usb_n, output wire pin_pu, input wire uart_rxd, output wire uart_txd) |

| module | uart (parameter DATA_WIDTH=8)(input wire clk |

| module | uart_rx (parameter DATA_WIDTH=8)(input wire clk |

| module | uart_tx (parameter DATA_WIDTH=8)(input wire clk |

| module char_buffer | ( | input wire | clk, |

| input wire< 7:0 > | din, | ||

| input wire< ADDR_BITS-1:0 > | waddr, | ||

| input wire | wen, | ||

| input wire< ADDR_BITS-1:0 > | raddr, | ||

| output reg< 7:0 > | dout, | ||

| input wire | graphic_mode | ||

| ) |

Char Buffer RAM (1920x8) (24 lines of 80 characters)

Definition at line 7 of file char_buffer.v.

References always().

Referenced by top().

| module char_rom | ( | input | clk, |

| input | addr[11:0], | ||

| output | dout_[8] | ||

| ) |

Character Font ROM (4kx8) This could be a RAM to allow font modifications, but not for now latin-1 subset of Terminus Font 8x16 (http://terminus-font.sourceforge.net) Terminus Font is licensed under the SIL Open Font License, Version 1.1.

The license is included as ofl.txt, and is also available with a FAQ at http://scripts.sil.org/OFL

Definition at line 9 of file char_rom.v.

References always().

Referenced by top().

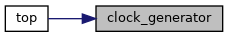

| module clock_generator | ( | input | clk, |

| output | clk_usb, | ||

| output | reset_usb, | ||

| output | clk_vga, | ||

| output | reset_vga | ||

| ) |

Definition at line 1 of file clock_generator.v.

References always().

Referenced by top().

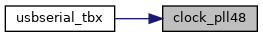

| module clock_pll48 | ( | input | clk_in, |

| output | clk_out, | ||

| output | clk_reset, | ||

| output | clk_tick | ||

| ) |

Definition at line 1 of file clock_pll48.v.

References always().

Referenced by usbserial_tbx().

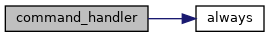

| module command_handler | ( | input | clk, |

| input | reset, | ||

| input | data[8], | ||

| input | valid, | ||

| output | ready, | ||

| output | new_first_char[ADDR_BITS-1:0], | ||

| output | new_first_char_wen, | ||

| output | new_char[8], | ||

| output | new_char_address[ADDR_BITS-1:0], | ||

| output | new_char_wen, | ||

| output | new_cursor_x[COL_BITS-1:0], | ||

| output | new_cursor_y[ROW_BITS-1:0], | ||

| output | new_cursor_wen, | ||

| output | graphic_mode | ||

| ) |

Definition at line 9 of file command_handler.v.

References always().

Referenced by top().

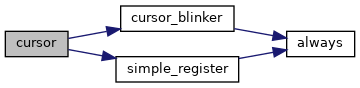

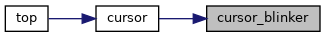

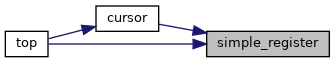

| module cursor | ( | input | clk, |

| input | reset, | ||

| input | tick, | ||

| output wire< COL_BITS-1:0 > | x, | ||

| output wire< ROW_BITS-1:0 > | y, | ||

| output wire | blink_on, | ||

| input | new_x[COL_BITS-1:0], | ||

| input | new_y[ROW_BITS-1:0], | ||

| input | wen | ||

| ) |

Cursor (position and blinking)

Definition at line 6 of file cursor.v.

References cursor_blinker(), and simple_register().

Referenced by top().

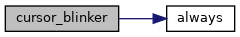

| module cursor_blinker | ( | input | clk, |

| input | reset, | ||

| input | tick, | ||

| input | reset_count, | ||

| output wire | blink_on | ||

| ) |

Cursor blinker (uses vblank as tick, blinks about once a second)

Definition at line 4 of file cursor_blinker.v.

References always().

Referenced by cursor().

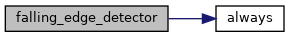

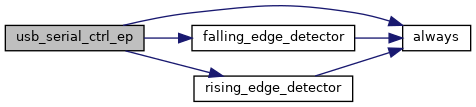

| module falling_edge_detector | ( | input | clk, |

| input | in, | ||

| output | out | ||

| ) |

Definition at line 15 of file edge_detect.v.

References always().

Referenced by usb_serial_ctrl_ep().

| module keyboard | ( | input | clk, |

| input | reset, | ||

| input | ps2_data, | ||

| input | ps2_clk, | ||

| output reg< 7:0 > | data, | ||

| output reg | valid, | ||

| input | ready | ||

| ) |

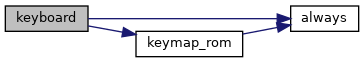

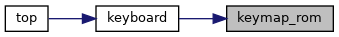

Definition at line 1 of file keyboard.v.

References always(), and keymap_rom().

Referenced by top().

| module keymap_rom | ( | input | clk, |

| input | addr[10:0], | ||

| output | dout_[8] | ||

| ) |

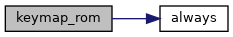

Keymap ROM (2KB, maps keycodes to ASCII chars) This could be a RAM to allow keymap modifications, but not for now There's 8 planes for each keycode (controlled by the highest three bits) MSB is for long keycode vs short keycode, the the next two bits: 00: no shift or caps lock 01: just shift 10: just caps lock 11: caps lock & shift.

Definition at line 11 of file keymap_rom.v.

References always().

Referenced by keyboard().

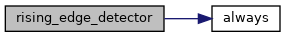

| module rising_edge_detector | ( | input | clk, |

| input | in, | ||

| output | out | ||

| ) |

Definition at line 1 of file edge_detect.v.

References always().

Referenced by usb_serial_ctrl_ep().

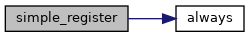

| module simple_register | ( | input wire | clk, |

| input wire | reset, | ||

| input wire< SIZE-1:0 > | idata, | ||

| input wire | wen, | ||

| output reg< SIZE-1:0 > | odata | ||

| ) |

Basic register with synchronous set & reset.

Definition at line 5 of file simple_register.v.

References always().

Referenced by cursor(), and top().

| module top | ( | input | pin_clk, |

| output wire | vga_clk, | ||

| output wire | vga_blank, | ||

| output wire | hsync, | ||

| output wire | vsync, | ||

| output wire< 7:0 > | vga_r, | ||

| output wire< 7:0 > | vga_g, | ||

| output wire< 7:0 > | vga_b, | ||

| output wire | pin_led, | ||

| input | ps2_data, | ||

| input | ps2_clk, | ||

| inout | pin_usb_p, | ||

| inout | pin_usb_n, | ||

| output wire | pin_pu, | ||

| input wire | uart_rxd, | ||

| output wire | uart_txd | ||

| ) |

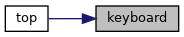

Definition at line 1 of file vt52.v.

References char_buffer(), char_rom(), clock_generator(), command_handler(), cursor(), keyboard(), m_axis_tdata, m_axis_tready, m_axis_tvalid, prescale, rst, rx_busy, rx_frame_error, rx_overrun_error, rxd, s_axis_tdata, s_axis_tready, s_axis_tvalid, simple_register(), tx_busy, txd, uart(), usb_uart(), and video_generator().

| module uart | ( | parameter | DATA_WIDTH = 8 | ) |

| module uart_rx | ( | parameter | DATA_WIDTH = 8 | ) |

| module uart_tx | ( | parameter | DATA_WIDTH = 8 | ) |

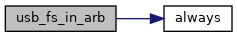

| module usb_fs_in_arb | ( | input | in_ep_req[NUM_IN_EPS-1:0], |

| output reg< NUM_IN_EPS-1:0 > | in_ep_grant, | ||

| input | in_ep_data[(NUM_IN_EPS *8) -1:0], | ||

| output reg< 7:0 > | arb_in_ep_data | ||

| ) |

| in_ep_req | ////////////////////////////////// |

| arb_in_ep_data | ////////////////////////////////// |

Definition at line 3 of file usb_fs_in_arb.v.

References always().

Referenced by usb_fs_pe().

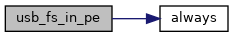

| module usb_fs_in_pe | ( | input | clk, |

| input | reset, | ||

| input | reset_ep[NUM_IN_EPS-1:0], | ||

| input | dev_addr[7], | ||

| output reg< NUM_IN_EPS-1:0 > | in_ep_data_free = 0, |

||

| input | in_ep_data_put[NUM_IN_EPS-1:0], | ||

| input | in_ep_data[8], | ||

| input | in_ep_data_done[NUM_IN_EPS-1:0], | ||

| input | in_ep_stall[NUM_IN_EPS-1:0], | ||

| output reg< NUM_IN_EPS-1:0 > | in_ep_acked = 0, |

||

| input | rx_pkt_start, | ||

| input | rx_pkt_end, | ||

| input | rx_pkt_valid, | ||

| input | rx_pid[4], | ||

| input | rx_addr[7], | ||

| input | rx_endp[4], | ||

| input | rx_frame_num[10:0], | ||

| output reg | tx_pkt_start = 0, |

||

| input | tx_pkt_end, | ||

| output reg< 3:0 > | tx_pid = 0, |

||

| output | tx_data_avail, | ||

| input | tx_data_get, | ||

| output reg< 7:0 > | tx_data, | ||

| output | debug[8] | ||

| ) |

| in_ep_data_free | ////////////////////////////////// |

| rx_pkt_start | ////////////////////////////////// |

| tx_pkt_start | ////////////////////////////////// |

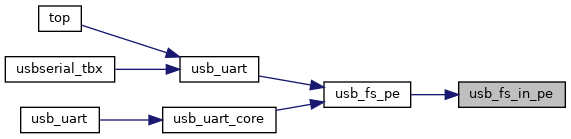

Definition at line 5 of file usb_fs_in_pe.v.

References always().

Referenced by usb_fs_pe().

| module usb_fs_out_arb | ( | input | out_ep_req[NUM_OUT_EPS-1:0], |

| output reg< NUM_OUT_EPS-1:0 > | out_ep_grant | ||

| ) |

| out_ep_req | ////////////////////////////////// |

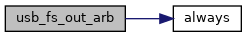

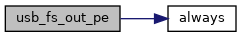

Definition at line 3 of file usb_fs_out_arb.v.

References always().

Referenced by usb_fs_pe().

| module usb_fs_out_pe | ( | input | clk, |

| input | reset, | ||

| input | reset_ep[NUM_OUT_EPS-1:0], | ||

| input | dev_addr[7], | ||

| output | out_ep_data_avail[NUM_OUT_EPS-1:0], | ||

| output reg< NUM_OUT_EPS-1:0 > | out_ep_setup = 0, |

||

| input | out_ep_data_get[NUM_OUT_EPS-1:0], | ||

| output reg< 7:0 > | out_ep_data, | ||

| input | out_ep_stall[NUM_OUT_EPS-1:0], | ||

| output reg< NUM_OUT_EPS-1:0 > | out_ep_acked = 0, |

||

| input | out_ep_grant[NUM_OUT_EPS-1:0], | ||

| input | rx_pkt_start, | ||

| input | rx_pkt_end, | ||

| input | rx_pkt_valid, | ||

| input | rx_pid[4], | ||

| input | rx_addr[7], | ||

| input | rx_endp[4], | ||

| input | rx_frame_num[10:0], | ||

| input | rx_data_put, | ||

| input | rx_data[8], | ||

| output reg | tx_pkt_start = 0, |

||

| input | tx_pkt_end, | ||

| output reg< 3:0 > | tx_pid = 0 |

||

| ) |

| out_ep_data_avail | ////////////////////////////////// |

| rx_pkt_start | ////////////////////////////////// |

| tx_pkt_start | ////////////////////////////////// |

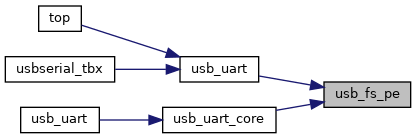

Definition at line 5 of file usb_fs_out_pe.v.

References always().

Referenced by usb_fs_pe().

| module usb_fs_pe | ( | input | clk, |

| input | dev_addr[7], | ||

| input | reset, | ||

| input | out_ep_req[NUM_OUT_EPS-1:0], | ||

| output | out_ep_grant[NUM_OUT_EPS-1:0], | ||

| output | out_ep_data_avail[NUM_OUT_EPS-1:0], | ||

| output | out_ep_setup[NUM_OUT_EPS-1:0], | ||

| input | out_ep_data_get[NUM_OUT_EPS-1:0], | ||

| output | out_ep_data[8], | ||

| input | out_ep_stall[NUM_OUT_EPS-1:0], | ||

| output | out_ep_acked[NUM_OUT_EPS-1:0], | ||

| input | in_ep_req[NUM_IN_EPS-1:0], | ||

| output | in_ep_grant[NUM_IN_EPS-1:0], | ||

| output | in_ep_data_free[NUM_IN_EPS-1:0], | ||

| input | in_ep_data_put[NUM_IN_EPS-1:0], | ||

| input | in_ep_data[(NUM_IN_EPS *8) -1:0], | ||

| input | in_ep_data_done[NUM_IN_EPS-1:0], | ||

| input | in_ep_stall[NUM_IN_EPS-1:0], | ||

| output | in_ep_acked[NUM_IN_EPS-1:0], | ||

| output | sof_valid, | ||

| output | frame_index[10:0], | ||

| output | usb_p_tx, | ||

| output | usb_n_tx, | ||

| input | usb_p_rx, | ||

| input | usb_n_rx, | ||

| output | usb_tx_en, | ||

| output | debug[8] | ||

| ) |

| reset | USB Endpoint Interface |

//////////////////////////////////

| out_ep_req | ////////////////////////////////// |

| in_ep_req | ////////////////////////////////// |

| sof_valid | ////////////////////////////////// |

| usb_p_tx | USB TX/RX Interface |

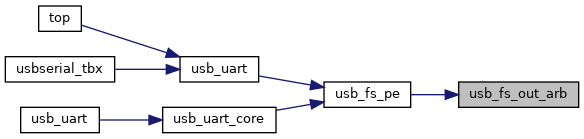

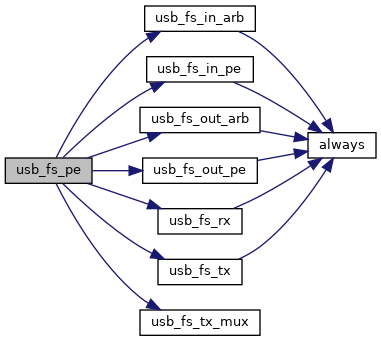

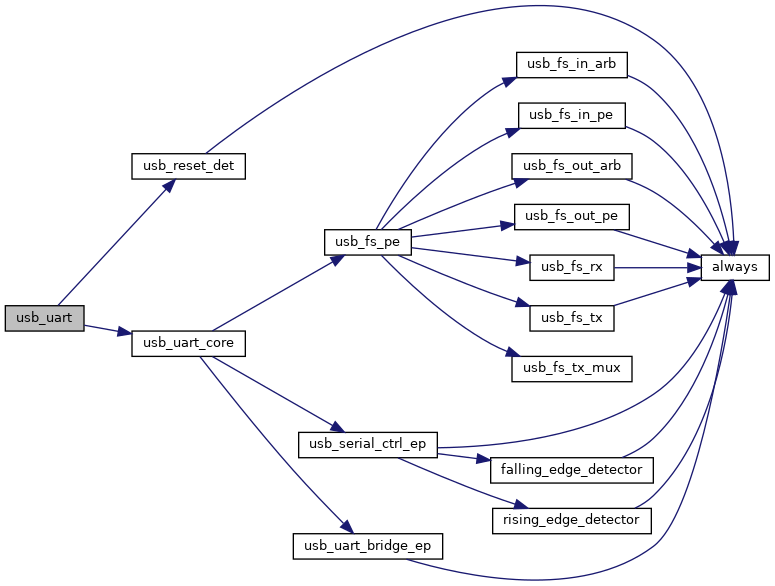

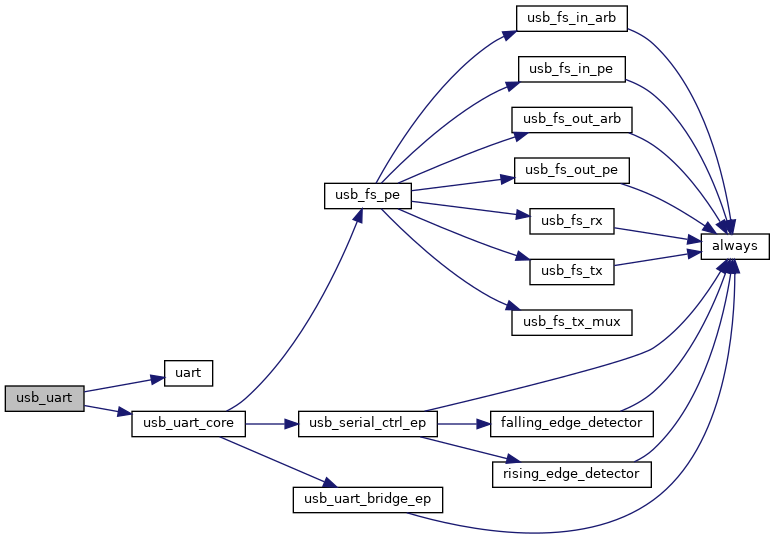

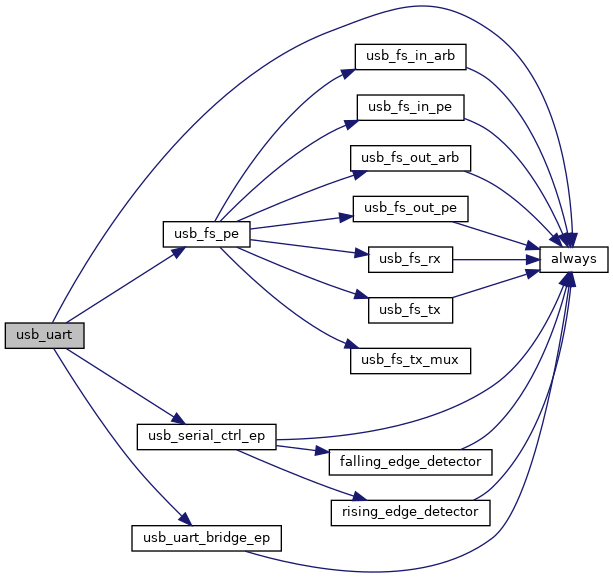

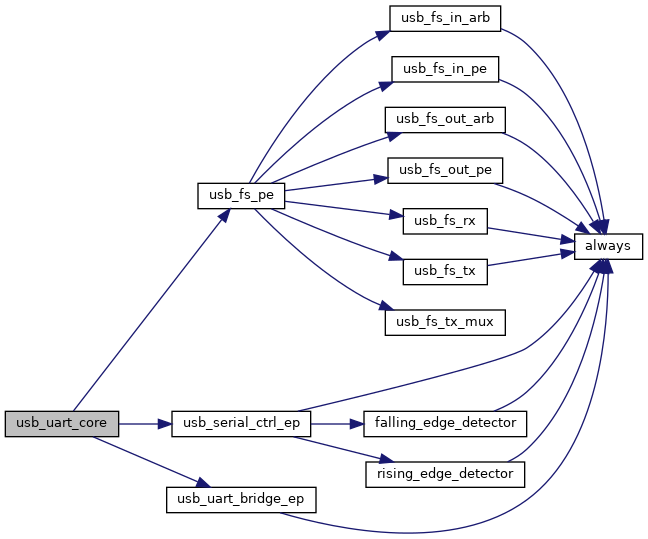

Definition at line 4 of file usb_fs_pe.v.

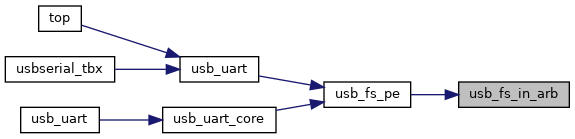

References usb_fs_in_arb(), usb_fs_in_pe(), usb_fs_out_arb(), usb_fs_out_pe(), usb_fs_rx(), usb_fs_tx(), and usb_fs_tx_mux().

Referenced by usb_uart(), and usb_uart_core().

| module usb_fs_rx | ( | input | clk_48mhz, |

| input | reset, | ||

| input | dp, | ||

| input | dn, | ||

| output | bit_strobe, | ||

| output | pkt_start, | ||

| output | pkt_end, | ||

| output | pid[4], | ||

| output reg< 6:0 > | addr = 0, |

||

| output reg< 3:0 > | endp = 0, |

||

| output reg< 10:0 > | frame_num = 0, |

||

| output | rx_data_put, | ||

| output | rx_data[8], | ||

| output | valid_packet | ||

| ) |

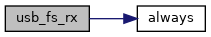

Definition at line 1 of file usb_fs_rx.v.

References always().

Referenced by usb_fs_pe().

| module usb_fs_tx | ( | input | clk_48mhz, |

| input | reset, | ||

| input | bit_strobe, | ||

| output reg | oe = 0, |

||

| output reg | dp = 0, |

||

| output reg | dn = 0, |

||

| input | pkt_start, | ||

| output | pkt_end, | ||

| input | pid[4], | ||

| input | tx_data_avail, | ||

| output reg | tx_data_get = 0, |

||

| input | tx_data[8] | ||

| ) |

Definition at line 1 of file usb_fs_tx.v.

References always().

Referenced by usb_fs_pe().

| module usb_fs_tx_mux | ( | input | in_tx_pkt_start, |

| input | in_tx_pid[4], | ||

| input | out_tx_pkt_start, | ||

| input | out_tx_pid[4], | ||

| output | tx_pkt_start, | ||

| output | tx_pid[4] | ||

| ) |

Definition at line 1 of file usb_fs_tx_mux.v.

Referenced by usb_fs_pe().

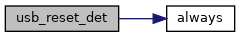

| module usb_reset_det | ( | input | clk, |

| output | reset, | ||

| input | usb_p_rx, | ||

| input | usb_n_rx | ||

| ) |

Definition at line 2 of file usb_reset_det.v.

References always().

Referenced by usb_uart().

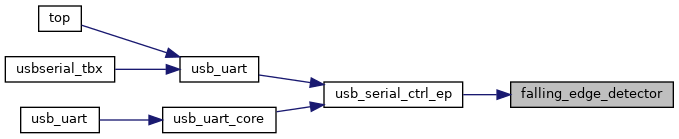

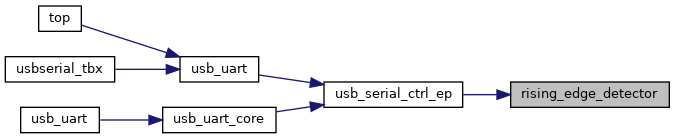

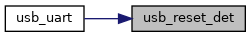

| module usb_serial_ctrl_ep | ( | input | clk, |

| input | reset, | ||

| output | dev_addr[7], | ||

| output | out_ep_req, | ||

| input | out_ep_grant, | ||

| input | out_ep_data_avail, | ||

| input | out_ep_setup, | ||

| output | out_ep_data_get, | ||

| input | out_ep_data[8], | ||

| output | out_ep_stall, | ||

| input | out_ep_acked, | ||

| output | in_ep_req, | ||

| input | in_ep_grant, | ||

| input | in_ep_data_free, | ||

| output | in_ep_data_put, | ||

| output reg< 7:0 > | in_ep_data = 0, |

||

| output | in_ep_data_done, | ||

| output reg | in_ep_stall, | ||

| input | in_ep_acked | ||

| ) |

| out_ep_req | ////////////////////////////////// |

| in_ep_req | ////////////////////////////////// |

Definition at line 4 of file usb_serial_ctrl_ep.v.

References always(), CDC_ACM_ENDPOINT, CDC_RX_ENDPOINT, CDC_TX_ENDPOINT, falling_edge_detector(), and rising_edge_detector().

Referenced by usb_uart(), and usb_uart_core().

| module usb_uart | ( | input | clk_48mhz, |

| input | reset, | ||

| inout | pin_usb_p, | ||

| inout | pin_usb_n, | ||

| inout | pipe_in[P_m(PipeSpec):0], | ||

| inout | pipe_out[P_m(PipeSpec):0], | ||

| output | debug[11:0] | ||

| ) |

Definition at line 34 of file usb_uart_ecp5.v.

References usb_uart_np().

| module usb_uart | ( | input | clk_48mhz, |

| input | reset, | ||

| inout | pin_usb_p, | ||

| inout | pin_usb_n, | ||

| input | uart_in_data[8], | ||

| input | uart_in_valid, | ||

| output | uart_in_ready, | ||

| output | uart_out_data[8], | ||

| output | uart_out_valid, | ||

| input | uart_out_ready, | ||

| output | det_reset, | ||

| output | debug[11:0] | ||

| ) |

Definition at line 35 of file usb_uart_x7.v.

References usb_reset_det(), and usb_uart_core().

| module usb_uart | ( | input | clk_48mhz, |

| input | reset, | ||

| inout | pin_usb_p, | ||

| inout | pin_usb_n, | ||

| input | uart_in_data[8], | ||

| input | uart_in_valid, | ||

| output | uart_in_ready, | ||

| output | uart_out_data[8], | ||

| output | uart_out_valid, | ||

| input | uart_out_ready, | ||

| output | debug[11:0] | ||

| ) |

Definition at line 31 of file usb_uart_i40.v.

References uart(), and usb_uart_core().

| module usb_uart | ( | input | clk_48mhz, |

| input | reset, | ||

| output | usb_p_tx, | ||

| output | usb_n_tx, | ||

| input | usb_p_rx, | ||

| input | usb_n_rx, | ||

| output | usb_tx_en, | ||

| input | uart_in_data[8], | ||

| input | uart_in_valid, | ||

| output | uart_in_ready, | ||

| output | uart_out_data[8], | ||

| output | uart_out_valid, | ||

| input | uart_out_ready, | ||

| output | debug[11:0] | ||

| ) |

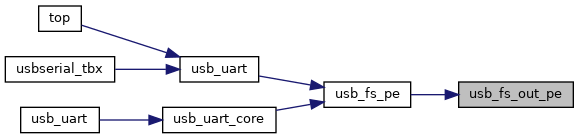

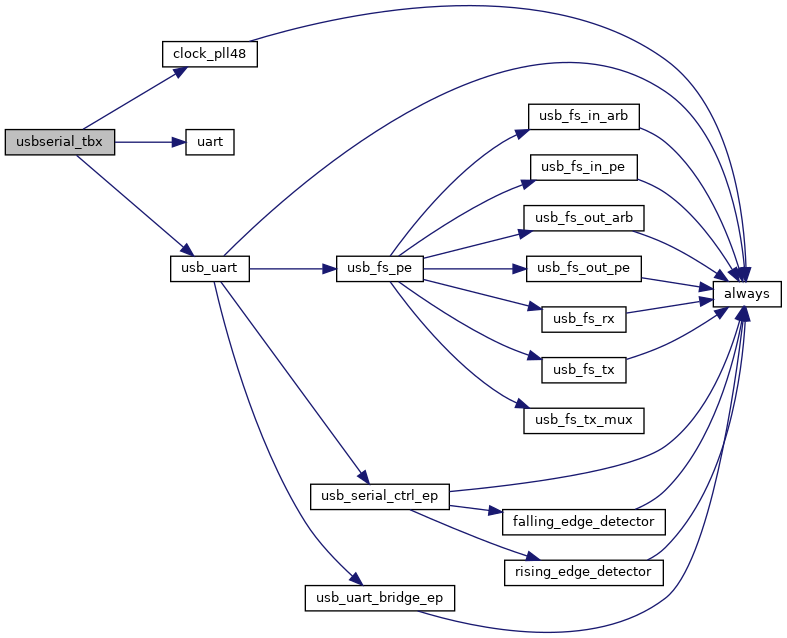

Definition at line 126 of file usb_uart.v.

References always(), usb_fs_pe(), usb_serial_ctrl_ep(), and usb_uart_bridge_ep().

Referenced by top(), and usbserial_tbx().

| module usb_uart_bridge_ep | ( | input | clk, |

| input | reset, | ||

| output | out_ep_req, | ||

| input | out_ep_grant, | ||

| input | out_ep_data_avail, | ||

| input | out_ep_setup, | ||

| output | out_ep_data_get, | ||

| input | out_ep_data[8], | ||

| output | out_ep_stall, | ||

| input | out_ep_acked, | ||

| output | in_ep_req, | ||

| input | in_ep_grant, | ||

| input | in_ep_data_free, | ||

| output | in_ep_data_put, | ||

| output | in_ep_data[8], | ||

| output | in_ep_data_done, | ||

| output | in_ep_stall, | ||

| input | in_ep_acked, | ||

| input | uart_in_data[8], | ||

| input | uart_in_valid, | ||

| output | uart_in_ready, | ||

| output | uart_out_data[8], | ||

| output | uart_out_valid, | ||

| input | uart_out_ready, | ||

| output | debug[4] | ||

| ) |

| out_ep_req | ////////////////////////////////// |

| in_ep_req | ////////////////////////////////// |

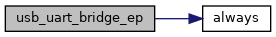

Definition at line 52 of file usb_uart_bridge_ep.v.

References always().

Referenced by usb_uart(), and usb_uart_core().

| module usb_uart_core | ( | input | clk_48mhz, |

| input | reset, | ||

| output | usb_p_tx, | ||

| output | usb_n_tx, | ||

| input | usb_p_rx, | ||

| input | usb_n_rx, | ||

| output | usb_tx_en, | ||

| input | uart_in_data[8], | ||

| input | uart_in_valid, | ||

| output | uart_in_ready, | ||

| output | uart_out_data[8], | ||

| output | uart_out_valid, | ||

| input | uart_out_ready, | ||

| output | debug[11:0] | ||

| ) |

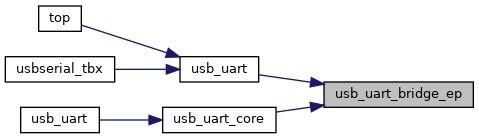

Definition at line 126 of file usb_uart_core.v.

References usb_fs_pe(), usb_serial_ctrl_ep(), and usb_uart_bridge_ep().

Referenced by usb_uart().

| module usb_uart_np | ( | input | clk_48mhz, |

| input | reset, | ||

| inout | pin_usb_p, | ||

| inout | pin_usb_n, | ||

| input | uart_in_data[8], | ||

| input | uart_in_valid, | ||

| output | uart_in_ready, | ||

| output | uart_out_data[8], | ||

| output | uart_out_valid, | ||

| input | uart_out_ready, | ||

| output | debug[11:0] | ||

| ) |

Definition at line 76 of file usb_uart_ecp5.v.

Referenced by usb_uart().

| module usbserial_tbx | ( | input | pin_clk, |

| inout | pin_usb_p, | ||

| inout | pin_usb_n, | ||

| output | pin_pu, | ||

| input | pin_button, | ||

| output | led_red, | ||

| output | led_green, | ||

| output | led_blue, | ||

| output | pin_led | ||

| ) |

Definition at line 7 of file usbserial_tbx.v.

References clock_pll48(), uart(), and usb_uart().

| module video_generator | ( | input | clk, |

| input | reset, | ||

| output reg | hsync, | ||

| output reg | vsync, | ||

| output reg | video, | ||

| output reg | hblank, | ||

| output reg | vblank, | ||

| input | cursor_x[COL_BITS-1:0], | ||

| input | cursor_y[ROW_BITS-1:0], | ||

| input | cursor_blink_on, | ||

| input | first_char[ADDR_BITS-1:0], | ||

| output wire< ADDR_BITS-1:0 > | char_buffer_address, | ||

| input | char_buffer_data[8], | ||

| output wire< 11:0 > | char_rom_address, | ||

| input | char_rom_data[8], | ||

| input | graphic_mode_state | ||

| ) |

80x24 char generator (8x16 char size) & sync generator

Definition at line 12 of file video_generator.v.

References always().

Referenced by top().

| module width_adapter | ( | input | clk, |

| input | reset, | ||

| input | data_in_put, | ||

| output | data_in_free, | ||

| input | data_in[INPUT_WIDTH-1:0], | ||

| output | data_out_put, | ||

| input | data_out_free, | ||

| output | data_out[OUTPUT_WIDTH-1:0] | ||

| ) |