|

SimpleVOut

1.0.0 Initial

A Simple FPGA Core for Creating VGA/DVI/HDMI/OpenLDI Signals

|

|

SimpleVOut

1.0.0 Initial

A Simple FPGA Core for Creating VGA/DVI/HDMI/OpenLDI Signals

|

Functions | |

| module | design_1_processing_system7_0_0 (ENET0_GMII_TX_EN, ENET0_GMII_TX_ER, ENET0_MDIO_MDC, ENET0_MDIO_O, ENET0_MDIO_T, ENET0_GMII_TXD, ENET0_GMII_COL, ENET0_GMII_CRS, ENET0_GMII_RX_CLK, ENET0_GMII_RX_DV, ENET0_GMII_RX_ER, ENET0_GMII_TX_CLK, ENET0_MDIO_I, ENET0_EXT_INTIN, ENET0_GMII_RXD, GPIO_I, GPIO_O, GPIO_T, TTC0_WAVE0_OUT, TTC0_WAVE1_OUT, TTC0_WAVE2_OUT, M_AXI_GP0_ARVALID, M_AXI_GP0_AWVALID, M_AXI_GP0_BREADY, M_AXI_GP0_RREADY, M_AXI_GP0_WLAST, M_AXI_GP0_WVALID, M_AXI_GP0_ARID, M_AXI_GP0_AWID, M_AXI_GP0_WID, M_AXI_GP0_ARBURST, M_AXI_GP0_ARLOCK, M_AXI_GP0_ARSIZE, M_AXI_GP0_AWBURST, M_AXI_GP0_AWLOCK, M_AXI_GP0_AWSIZE, M_AXI_GP0_ARPROT, M_AXI_GP0_AWPROT, M_AXI_GP0_ARADDR, M_AXI_GP0_AWADDR, M_AXI_GP0_WDATA, M_AXI_GP0_ARCACHE, M_AXI_GP0_ARLEN, M_AXI_GP0_ARQOS, M_AXI_GP0_AWCACHE, M_AXI_GP0_AWLEN, M_AXI_GP0_AWQOS, M_AXI_GP0_WSTRB, M_AXI_GP0_ACLK, M_AXI_GP0_ARREADY, M_AXI_GP0_AWREADY, M_AXI_GP0_BVALID, M_AXI_GP0_RLAST, M_AXI_GP0_RVALID, M_AXI_GP0_WREADY, M_AXI_GP0_BID, M_AXI_GP0_RID, M_AXI_GP0_BRESP, M_AXI_GP0_RRESP, M_AXI_GP0_RDATA, S_AXI_HP0_ARREADY, S_AXI_HP0_AWREADY, S_AXI_HP0_BVALID, S_AXI_HP0_RLAST, S_AXI_HP0_RVALID, S_AXI_HP0_WREADY, S_AXI_HP0_BRESP, S_AXI_HP0_RRESP, S_AXI_HP0_BID, S_AXI_HP0_RID, S_AXI_HP0_RDATA, S_AXI_HP0_RCOUNT, S_AXI_HP0_WCOUNT, S_AXI_HP0_RACOUNT, S_AXI_HP0_WACOUNT, S_AXI_HP0_ACLK, S_AXI_HP0_ARVALID, S_AXI_HP0_AWVALID, S_AXI_HP0_BREADY, S_AXI_HP0_RDISSUECAP1_EN, S_AXI_HP0_RREADY, S_AXI_HP0_WLAST, S_AXI_HP0_WRISSUECAP1_EN, S_AXI_HP0_WVALID, S_AXI_HP0_ARBURST, S_AXI_HP0_ARLOCK, S_AXI_HP0_ARSIZE, S_AXI_HP0_AWBURST, S_AXI_HP0_AWLOCK, S_AXI_HP0_AWSIZE, S_AXI_HP0_ARPROT, S_AXI_HP0_AWPROT, S_AXI_HP0_ARADDR, S_AXI_HP0_AWADDR, S_AXI_HP0_ARCACHE, S_AXI_HP0_ARLEN, S_AXI_HP0_ARQOS, S_AXI_HP0_AWCACHE, S_AXI_HP0_AWLEN, S_AXI_HP0_AWQOS, S_AXI_HP0_ARID, S_AXI_HP0_AWID, S_AXI_HP0_WID, S_AXI_HP0_WDATA, S_AXI_HP0_WSTRB, IRQ_F2P, FCLK_CLK0, FCLK_CLK1, FCLK_CLK2, FCLK_CLK3, FCLK_RESET0_N, MIO, DDR_CAS_n, DDR_CKE, DDR_Clk_n, DDR_Clk, DDR_CS_n, DDR_DRSTB, DDR_ODT, DDR_RAS_n, DDR_WEB, DDR_BankAddr, DDR_Addr, DDR_VRN, DDR_VRP, DDR_DM, DDR_DQ, DDR_DQS_n, DDR_DQS, PS_SRSTB, PS_CLK, PS_PORB) |

| module | processing_system7_vip_v1_0_10_arb_wr (rstn, sw_clk, qos1, qos2, prt_dv1, prt_dv2, prt_data1, prt_data2, prt_addr1, prt_addr2, prt_bytes1, prt_bytes2, prt_strb1, prt_strb2, prt_ack1, prt_ack2, prt_qos, prt_req, prt_data, prt_strb, prt_addr, prt_bytes, prt_ack) |

| module | processing_system7_vip_v1_0_10_arb_rd (rstn, sw_clk, qos1, qos2, prt_req1, prt_req2, prt_bytes1, prt_bytes2, prt_addr1, prt_addr2, prt_data1, prt_data2, prt_dv1, prt_dv2, prt_req, prt_qos, prt_addr, prt_bytes, prt_data, prt_dv) |

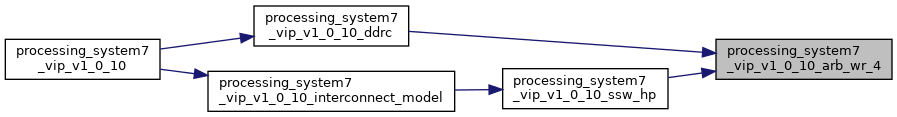

| module | processing_system7_vip_v1_0_10_arb_wr_4 (rstn, sw_clk, qos1, qos2, qos3, qos4, prt_dv1, prt_dv2, prt_dv3, prt_dv4, prt_data1, prt_data2, prt_data3, prt_data4, prt_strb1, prt_strb2, prt_strb3, prt_strb4, prt_addr1, prt_addr2, prt_addr3, prt_addr4, prt_bytes1, prt_bytes2, prt_bytes3, prt_bytes4, prt_ack1, prt_ack2, prt_ack3, prt_ack4, prt_qos, prt_req, prt_data, prt_strb, prt_addr, prt_bytes, prt_ack) |

| module | processing_system7_vip_v1_0_10_arb_rd_4 (rstn, sw_clk, qos1, qos2, qos3, qos4, prt_req1, prt_req2, prt_req3, prt_req4, prt_data1, prt_data2, prt_data3, prt_data4, prt_addr1, prt_addr2, prt_addr3, prt_addr4, prt_bytes1, prt_bytes2, prt_bytes3, prt_bytes4, prt_dv1, prt_dv2, prt_dv3, prt_dv4, prt_qos, prt_req, prt_data, prt_addr, prt_bytes, prt_dv) |

| module | processing_system7_vip_v1_0_10_arb_hp2_3 (sw_clk, rstn, w_qos_hp2, r_qos_hp2, w_qos_hp3, r_qos_hp3, wr_ack_ddr_hp2, wr_data_hp2, wr_strb_hp2, wr_addr_hp2, wr_bytes_hp2, wr_dv_ddr_hp2, rd_req_ddr_hp2, rd_addr_hp2, rd_bytes_hp2, rd_data_ddr_hp2, rd_dv_ddr_hp2, wr_ack_ddr_hp3, wr_data_hp3, wr_strb_hp3, wr_addr_hp3, wr_bytes_hp3, wr_dv_ddr_hp3, rd_req_ddr_hp3, rd_addr_hp3, rd_bytes_hp3, rd_data_ddr_hp3, rd_dv_ddr_hp3, ddr_wr_ack, ddr_wr_dv, ddr_rd_req, ddr_rd_dv, ddr_rd_qos, ddr_wr_qos, ddr_wr_addr, ddr_wr_data, ddr_wr_strb, ddr_wr_bytes, ddr_rd_addr, ddr_rd_data, ddr_rd_bytes) |

| module | processing_system7_vip_v1_0_10_arb_hp0_1 (sw_clk, rstn, w_qos_hp0, r_qos_hp0, w_qos_hp1, r_qos_hp1, wr_ack_ddr_hp0, wr_data_hp0, wr_strb_hp0, wr_addr_hp0, wr_bytes_hp0, wr_dv_ddr_hp0, rd_req_ddr_hp0, rd_addr_hp0, rd_bytes_hp0, rd_data_ddr_hp0, rd_dv_ddr_hp0, wr_ack_ddr_hp1, wr_data_hp1, wr_strb_hp1, wr_addr_hp1, wr_bytes_hp1, wr_dv_ddr_hp1, rd_req_ddr_hp1, rd_addr_hp1, rd_bytes_hp1, rd_data_ddr_hp1, rd_dv_ddr_hp1, ddr_wr_ack, ddr_wr_dv, ddr_rd_req, ddr_rd_dv, ddr_rd_qos, ddr_wr_qos, ddr_wr_addr, ddr_wr_data, ddr_wr_strb, ddr_wr_bytes, ddr_rd_addr, ddr_rd_data, ddr_rd_bytes) |

| module | processing_system7_vip_v1_0_10_ssw_hp (sw_clk, rstn, w_qos_hp0, r_qos_hp0, w_qos_hp1, r_qos_hp1, w_qos_hp2, r_qos_hp2, w_qos_hp3, r_qos_hp3, wr_ack_ddr_hp0, wr_data_hp0, wr_strb_hp0, wr_addr_hp0, wr_bytes_hp0, wr_dv_ddr_hp0, rd_req_ddr_hp0, rd_addr_hp0, rd_bytes_hp0, rd_data_ddr_hp0, rd_dv_ddr_hp0, rd_data_ocm_hp0, wr_ack_ocm_hp0, wr_dv_ocm_hp0, rd_req_ocm_hp0, rd_dv_ocm_hp0, wr_ack_ddr_hp1, wr_data_hp1, wr_strb_hp1, wr_addr_hp1, wr_bytes_hp1, wr_dv_ddr_hp1, rd_req_ddr_hp1, rd_addr_hp1, rd_bytes_hp1, rd_data_ddr_hp1, rd_data_ocm_hp1, rd_dv_ddr_hp1, wr_ack_ocm_hp1, wr_dv_ocm_hp1, rd_req_ocm_hp1, rd_dv_ocm_hp1, wr_ack_ddr_hp2, wr_data_hp2, wr_strb_hp2, wr_addr_hp2, wr_bytes_hp2, wr_dv_ddr_hp2, rd_req_ddr_hp2, rd_addr_hp2, rd_bytes_hp2, rd_data_ddr_hp2, rd_data_ocm_hp2, rd_dv_ddr_hp2, wr_ack_ocm_hp2, wr_dv_ocm_hp2, rd_req_ocm_hp2, rd_dv_ocm_hp2, wr_ack_ddr_hp3, wr_data_hp3, wr_strb_hp3, wr_addr_hp3, wr_bytes_hp3, wr_dv_ddr_hp3, rd_req_ddr_hp3, rd_addr_hp3, rd_bytes_hp3, rd_data_ocm_hp3, rd_data_ddr_hp3, rd_dv_ddr_hp3, wr_ack_ocm_hp3, wr_dv_ocm_hp3, rd_req_ocm_hp3, rd_dv_ocm_hp3, ddr_wr_ack0, ddr_wr_dv0, ddr_rd_req0, ddr_rd_dv0, ddr_rd_qos0, ddr_wr_qos0, ddr_wr_addr0, ddr_wr_data0, ddr_wr_strb0, ddr_wr_bytes0, ddr_rd_addr0, ddr_rd_data0, ddr_rd_bytes0, ddr_wr_ack1, ddr_wr_dv1, ddr_rd_req1, ddr_rd_dv1, ddr_rd_qos1, ddr_wr_qos1, ddr_wr_addr1, ddr_wr_data1, ddr_wr_strb1, ddr_wr_bytes1, ddr_rd_addr1, ddr_rd_data1, ddr_rd_bytes1, ocm_wr_ack, ocm_wr_dv, ocm_rd_req, ocm_rd_dv, ocm_wr_qos, ocm_rd_qos, ocm_wr_addr, ocm_wr_data, ocm_wr_strb, ocm_wr_bytes, ocm_rd_addr, ocm_rd_data, ocm_rd_bytes) |

| module | processing_system7_vip_v1_0_10_sparse_mem () |

| module | processing_system7_vip_v1_0_10_reg_map () |

| module | processing_system7_vip_v1_0_10_ocm_mem () |

| module | processing_system7_vip_v1_0_10_intr_wr_mem (sw_clk, rstn, full, WR_DATA_ACK_OCM, WR_DATA_ACK_DDR, WR_ADDR, WR_DATA, WR_BYTES, WR_QOS, WR_DATA_VALID_OCM, WR_DATA_VALID_DDR) |

| module | processing_system7_vip_v1_0_10_intr_rd_mem (sw_clk, rstn, full, empty, req, invalid_rd_req, rd_info, RD_DATA_OCM, RD_DATA_DDR, RD_DATA_VALID_OCM, RD_DATA_VALID_DDR) |

| module | processing_system7_vip_v1_0_10_fmsw_gp (sw_clk, rstn, w_qos_gp0, r_qos_gp0, wr_ack_ocm_gp0, wr_ack_ddr_gp0, wr_data_gp0, wr_strb_gp0, wr_addr_gp0, wr_bytes_gp0, wr_dv_ocm_gp0, wr_dv_ddr_gp0, rd_req_ocm_gp0, rd_req_ddr_gp0, rd_req_reg_gp0, rd_addr_gp0, rd_bytes_gp0, rd_data_ocm_gp0, rd_data_ddr_gp0, rd_data_reg_gp0, rd_dv_ocm_gp0, rd_dv_ddr_gp0, rd_dv_reg_gp0, w_qos_gp1, r_qos_gp1, wr_ack_ocm_gp1, wr_ack_ddr_gp1, wr_data_gp1, wr_strb_gp1, wr_addr_gp1, wr_bytes_gp1, wr_dv_ocm_gp1, wr_dv_ddr_gp1, rd_req_ocm_gp1, rd_req_ddr_gp1, rd_req_reg_gp1, rd_addr_gp1, rd_bytes_gp1, rd_data_ocm_gp1, rd_data_ddr_gp1, rd_data_reg_gp1, rd_dv_ocm_gp1, rd_dv_ddr_gp1, rd_dv_reg_gp1, ocm_wr_ack, ocm_wr_dv, ocm_rd_req, ocm_rd_dv, ddr_wr_ack, ddr_wr_dv, ddr_rd_req, ddr_rd_dv, reg_rd_req, reg_rd_dv, ocm_wr_qos, ddr_wr_qos, ocm_rd_qos, ddr_rd_qos, reg_rd_qos, ocm_wr_addr, ocm_wr_data, ocm_wr_strb, ocm_wr_bytes, ocm_rd_addr, ocm_rd_data, ocm_rd_bytes, ddr_wr_addr, ddr_wr_data, ddr_wr_strb, ddr_wr_bytes, ddr_rd_addr, ddr_rd_data, ddr_rd_bytes, reg_rd_addr, reg_rd_data, reg_rd_bytes) |

| module | processing_system7_vip_v1_0_10_regc (rstn, sw_clk, reg_rd_req_port0, reg_rd_dv_port0, reg_rd_addr_port0, reg_rd_data_port0, reg_rd_bytes_port0, reg_rd_qos_port0, reg_rd_req_port1, reg_rd_dv_port1, reg_rd_addr_port1, reg_rd_data_port1, reg_rd_bytes_port1, reg_rd_qos_port1) |

| module | processing_system7_vip_v1_0_10_ocmc (rstn, sw_clk, ocm_wr_ack_port0, ocm_wr_dv_port0, ocm_rd_req_port0, ocm_rd_dv_port0, ocm_wr_addr_port0, ocm_wr_data_port0, ocm_wr_strb_port0, ocm_wr_bytes_port0, ocm_rd_addr_port0, ocm_rd_data_port0, ocm_rd_bytes_port0, ocm_wr_qos_port0, ocm_rd_qos_port0, ocm_wr_ack_port1, ocm_wr_dv_port1, ocm_rd_req_port1, ocm_rd_dv_port1, ocm_wr_addr_port1, ocm_wr_data_port1, ocm_wr_strb_port1, ocm_wr_bytes_port1, ocm_rd_addr_port1, ocm_rd_data_port1, ocm_rd_bytes_port1, ocm_wr_qos_port1, ocm_rd_qos_port1) |

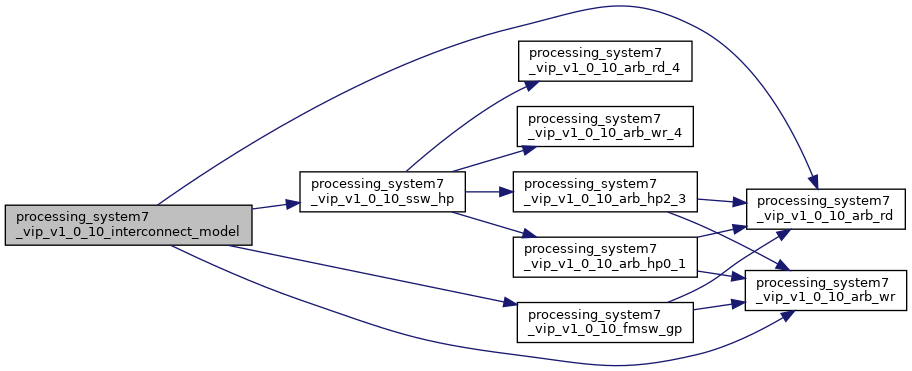

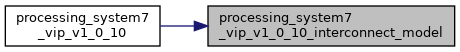

| module | processing_system7_vip_v1_0_10_interconnect_model (rstn, sw_clk, w_qos_gp0, w_qos_gp1, w_qos_hp0, w_qos_hp1, w_qos_hp2, w_qos_hp3, r_qos_gp0, r_qos_gp1, r_qos_hp0, r_qos_hp1, r_qos_hp2, r_qos_hp3, wr_ack_ddr_gp0, wr_ack_ocm_gp0, wr_data_gp0, wr_strb_gp0, wr_addr_gp0, wr_bytes_gp0, wr_dv_ddr_gp0, wr_dv_ocm_gp0, rd_req_ddr_gp0, rd_req_ocm_gp0, rd_req_reg_gp0, rd_addr_gp0, rd_bytes_gp0, rd_data_ddr_gp0, rd_data_ocm_gp0, rd_data_reg_gp0, rd_dv_ddr_gp0, rd_dv_ocm_gp0, rd_dv_reg_gp0, wr_ack_ddr_gp1, wr_ack_ocm_gp1, wr_data_gp1, wr_strb_gp1, wr_addr_gp1, wr_bytes_gp1, wr_dv_ddr_gp1, wr_dv_ocm_gp1, rd_req_ddr_gp1, rd_req_ocm_gp1, rd_req_reg_gp1, rd_addr_gp1, rd_bytes_gp1, rd_data_ddr_gp1, rd_data_ocm_gp1, rd_data_reg_gp1, rd_dv_ddr_gp1, rd_dv_ocm_gp1, rd_dv_reg_gp1, wr_ack_ddr_hp0, wr_ack_ocm_hp0, wr_data_hp0, wr_strb_hp0, wr_addr_hp0, wr_bytes_hp0, wr_dv_ddr_hp0, wr_dv_ocm_hp0, rd_req_ddr_hp0, rd_req_ocm_hp0, rd_addr_hp0, rd_bytes_hp0, rd_data_ddr_hp0, rd_data_ocm_hp0, rd_dv_ddr_hp0, rd_dv_ocm_hp0, wr_ack_ddr_hp1, wr_ack_ocm_hp1, wr_data_hp1, wr_strb_hp1, wr_addr_hp1, wr_bytes_hp1, wr_dv_ddr_hp1, wr_dv_ocm_hp1, rd_req_ddr_hp1, rd_req_ocm_hp1, rd_addr_hp1, rd_bytes_hp1, rd_data_ddr_hp1, rd_data_ocm_hp1, rd_dv_ddr_hp1, rd_dv_ocm_hp1, wr_ack_ddr_hp2, wr_ack_ocm_hp2, wr_data_hp2, wr_strb_hp2, wr_addr_hp2, wr_bytes_hp2, wr_dv_ddr_hp2, wr_dv_ocm_hp2, rd_req_ddr_hp2, rd_req_ocm_hp2, rd_addr_hp2, rd_bytes_hp2, rd_data_ddr_hp2, rd_data_ocm_hp2, rd_dv_ddr_hp2, rd_dv_ocm_hp2, wr_ack_ddr_hp3, wr_ack_ocm_hp3, wr_data_hp3, wr_strb_hp3, wr_addr_hp3, wr_bytes_hp3, wr_dv_ddr_hp3, wr_dv_ocm_hp3, rd_req_ddr_hp3, rd_req_ocm_hp3, rd_addr_hp3, rd_bytes_hp3, rd_data_ddr_hp3, rd_data_ocm_hp3, rd_dv_ddr_hp3, rd_dv_ocm_hp3, ddr_wr_ack_port1, ddr_wr_dv_port1, ddr_rd_req_port1, ddr_rd_dv_port1, ddr_wr_addr_port1, ddr_wr_data_port1, ddr_wr_strb_port1, ddr_wr_bytes_port1, ddr_rd_addr_port1, ddr_rd_data_port1, ddr_rd_bytes_port1, ddr_wr_qos_port1, ddr_rd_qos_port1, ddr_wr_ack_port2, ddr_wr_dv_port2, ddr_rd_req_port2, ddr_rd_dv_port2, ddr_wr_addr_port2, ddr_wr_data_port2, ddr_wr_strb_port2, ddr_wr_bytes_port2, ddr_rd_addr_port2, ddr_rd_data_port2, ddr_rd_bytes_port2, ddr_wr_qos_port2, ddr_rd_qos_port2, ddr_wr_ack_port3, ddr_wr_dv_port3, ddr_rd_req_port3, ddr_rd_dv_port3, ddr_wr_addr_port3, ddr_wr_data_port3, ddr_wr_strb_port3, ddr_wr_bytes_port3, ddr_rd_addr_port3, ddr_rd_data_port3, ddr_rd_bytes_port3, ddr_wr_qos_port3, ddr_rd_qos_port3, ocm_wr_qos_port1, ocm_rd_qos_port1, ocm_wr_dv_port1, ocm_wr_data_port1, ocm_wr_strb_port1, ocm_wr_addr_port1, ocm_wr_bytes_port1, ocm_wr_ack_port1, ocm_rd_req_port1, ocm_rd_data_port1, ocm_rd_addr_port1, ocm_rd_bytes_port1, ocm_rd_dv_port1, reg_rd_qos_port1, reg_rd_req_port1, reg_rd_data_port1, reg_rd_addr_port1, reg_rd_bytes_port1, reg_rd_dv_port1) |

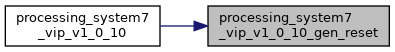

| module | processing_system7_vip_v1_0_10_gen_reset (por_rst_n, sys_rst_n, rst_out_n, m_axi_gp0_clk, m_axi_gp1_clk, s_axi_gp0_clk, s_axi_gp1_clk, s_axi_hp0_clk, s_axi_hp1_clk, s_axi_hp2_clk, s_axi_hp3_clk, s_axi_acp_clk, m_axi_gp0_rstn, m_axi_gp1_rstn, s_axi_gp0_rstn, s_axi_gp1_rstn, s_axi_hp0_rstn, s_axi_hp1_rstn, s_axi_hp2_rstn, s_axi_hp3_rstn, s_axi_acp_rstn, fclk_reset3_n, fclk_reset2_n, fclk_reset1_n, fclk_reset0_n, fpga_acp_reset_n, fpga_gp_m0_reset_n, fpga_gp_m1_reset_n, fpga_gp_s0_reset_n, fpga_gp_s1_reset_n, fpga_hp_s0_reset_n, fpga_hp_s1_reset_n, fpga_hp_s2_reset_n, fpga_hp_s3_reset_n) |

| module | processing_system7_vip_v1_0_10_gen_clock (ps_clk, sw_clk, fclk_clk3, fclk_clk2, fclk_clk1, fclk_clk0) |

| module | processing_system7_vip_v1_0_10_ddrc (rstn, sw_clk, ddr_wr_ack_port0, ddr_wr_dv_port0, ddr_rd_req_port0, ddr_rd_dv_port0, ddr_wr_addr_port0, ddr_wr_data_port0, ddr_wr_strb_port0, ddr_wr_bytes_port0, ddr_rd_addr_port0, ddr_rd_data_port0, ddr_rd_bytes_port0, ddr_wr_qos_port0, ddr_rd_qos_port0, ddr_wr_ack_port1, ddr_wr_dv_port1, ddr_rd_req_port1, ddr_rd_dv_port1, ddr_wr_addr_port1, ddr_wr_data_port1, ddr_wr_strb_port1, ddr_wr_bytes_port1, ddr_rd_addr_port1, ddr_rd_data_port1, ddr_rd_bytes_port1, ddr_wr_qos_port1, ddr_rd_qos_port1, ddr_wr_ack_port2, ddr_wr_dv_port2, ddr_rd_req_port2, ddr_rd_dv_port2, ddr_wr_addr_port2, ddr_wr_data_port2, ddr_wr_strb_port2, ddr_wr_bytes_port2, ddr_rd_addr_port2, ddr_rd_data_port2, ddr_rd_bytes_port2, ddr_wr_qos_port2, ddr_rd_qos_port2, ddr_wr_ack_port3, ddr_wr_dv_port3, ddr_rd_req_port3, ddr_rd_dv_port3, ddr_wr_addr_port3, ddr_wr_data_port3, ddr_wr_strb_port3, ddr_wr_bytes_port3, ddr_rd_addr_port3, ddr_rd_data_port3, ddr_rd_bytes_port3, ddr_wr_qos_port3, ddr_rd_qos_port3) |

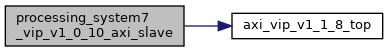

| module | processing_system7_vip_v1_0_10_axi_slave (S_RESETN, S_ARREADY, S_AWREADY, S_BVALID, S_RLAST, S_RVALID, S_WREADY, S_BRESP, S_RRESP, S_RDATA, S_BID, S_RID, S_ACLK, S_ARVALID, S_AWVALID, S_BREADY, S_RREADY, S_WLAST, S_WVALID, S_ARBURST, S_ARLOCK, S_ARSIZE, S_AWBURST, S_AWLOCK, S_AWSIZE, S_ARPROT, S_AWPROT, S_ARADDR, S_AWADDR, S_WDATA, S_ARCACHE, S_ARLEN, S_AWCACHE, S_AWLEN, S_WSTRB, S_ARID, S_AWID, S_WID, S_AWQOS, S_ARQOS, SW_CLK, WR_DATA_ACK_OCM, WR_DATA_ACK_DDR, WR_ADDR, WR_DATA, WR_DATA_STRB, WR_BYTES, WR_DATA_VALID_OCM, WR_DATA_VALID_DDR, WR_QOS, RD_QOS, RD_REQ_DDR, RD_REQ_OCM, RD_REQ_REG, RD_ADDR, RD_DATA_OCM, RD_DATA_DDR, RD_DATA_REG, RD_BYTES, RD_DATA_VALID_OCM, RD_DATA_VALID_DDR, RD_DATA_VALID_REG) |

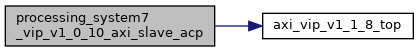

| module | processing_system7_vip_v1_0_10_axi_slave_acp (S_RESETN, S_ARREADY, S_AWREADY, S_BVALID, S_RLAST, S_RVALID, S_WREADY, S_BRESP, S_RRESP, S_RDATA, S_BID, S_RID, S_ACLK, S_ARVALID, S_AWVALID, S_BREADY, S_RREADY, S_WLAST, S_WVALID, S_ARBURST, S_ARLOCK, S_ARSIZE, S_AWBURST, S_AWLOCK, S_AWSIZE, S_ARPROT, S_AWPROT, S_ARADDR, S_AWADDR, S_WDATA, S_ARCACHE, S_ARLEN, S_AWCACHE, S_AWLEN, S_WSTRB, S_ARID, S_AWID, S_WID, S_AWQOS, S_ARQOS, SW_CLK, WR_DATA_ACK_OCM, WR_DATA_ACK_DDR, WR_ADDR, WR_DATA, WR_DATA_STRB, WR_BYTES, WR_DATA_VALID_OCM, WR_DATA_VALID_DDR, WR_QOS, RD_QOS, RD_REQ_DDR, RD_REQ_OCM, RD_REQ_REG, RD_ADDR, RD_DATA_OCM, RD_DATA_DDR, RD_DATA_REG, RD_BYTES, RD_DATA_VALID_OCM, RD_DATA_VALID_DDR, RD_DATA_VALID_REG) |

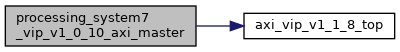

| module | processing_system7_vip_v1_0_10_axi_master (M_RESETN, M_ARVALID, M_AWVALID, M_BREADY, M_RREADY, M_WLAST, M_WVALID, M_ARID, M_AWID, M_WID, M_ARBURST, M_ARLOCK, M_ARSIZE, M_AWBURST, M_AWLOCK, M_AWSIZE, M_ARPROT, M_AWPROT, M_ARADDR, M_AWADDR, M_WDATA, M_ARCACHE, M_ARLEN, M_AWCACHE, M_AWLEN, M_ARQOS, M_AWQOS, M_WSTRB, M_ACLK, M_ARREADY, M_AWREADY, M_BVALID, M_RLAST, M_RVALID, M_WREADY, M_BID, M_RID, M_BRESP, M_RRESP, M_RDATA) |

| module | processing_system7_vip_v1_0_10_afi_slave (S_RESETN, S_ARREADY, S_AWREADY, S_BVALID, S_RLAST, S_RVALID, S_WREADY, S_BRESP, S_RRESP, S_RDATA, S_BID, S_RID, S_ACLK, S_ARVALID, S_AWVALID, S_BREADY, S_RREADY, S_WLAST, S_WVALID, S_ARBURST, S_ARLOCK, S_ARSIZE, S_AWBURST, S_AWLOCK, S_AWSIZE, S_ARPROT, S_AWPROT, S_ARADDR, S_AWADDR, S_WDATA, S_ARCACHE, S_ARLEN, S_AWCACHE, S_AWLEN, S_WSTRB, S_ARID, S_AWID, S_WID, S_AWQOS, S_ARQOS, SW_CLK, WR_DATA_ACK_OCM, WR_DATA_ACK_DDR, WR_ADDR, WR_DATA, WR_BYTES, WR_DATA_STRB, WR_DATA_VALID_OCM, WR_DATA_VALID_DDR, WR_QOS, RD_REQ_DDR, RD_REQ_OCM, RD_ADDR, RD_DATA_OCM, RD_DATA_DDR, RD_BYTES, RD_QOS, RD_DATA_VALID_OCM, RD_DATA_VALID_DDR, S_RDISSUECAP1_EN, S_WRISSUECAP1_EN, S_RCOUNT, S_WCOUNT, S_RACOUNT, S_WACOUNT) |

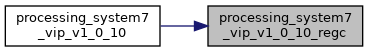

| module | processing_system7_vip_v1_0_10 (CAN0_PHY_TX, CAN0_PHY_RX, CAN1_PHY_TX, CAN1_PHY_RX, ENET0_GMII_TX_EN, ENET0_GMII_TX_ER, ENET0_MDIO_MDC, ENET0_MDIO_O, ENET0_MDIO_T, ENET0_PTP_DELAY_REQ_RX, ENET0_PTP_DELAY_REQ_TX, ENET0_PTP_PDELAY_REQ_RX, ENET0_PTP_PDELAY_REQ_TX, ENET0_PTP_PDELAY_RESP_RX, ENET0_PTP_PDELAY_RESP_TX, ENET0_PTP_SYNC_FRAME_RX, ENET0_PTP_SYNC_FRAME_TX, ENET0_SOF_RX, ENET0_SOF_TX, ENET0_GMII_TXD, ENET0_GMII_COL, ENET0_GMII_CRS, ENET0_EXT_INTIN, ENET0_GMII_RX_CLK, ENET0_GMII_RX_DV, ENET0_GMII_RX_ER, ENET0_GMII_TX_CLK, ENET0_MDIO_I, ENET0_GMII_RXD, ENET1_GMII_TX_EN, ENET1_GMII_TX_ER, ENET1_MDIO_MDC, ENET1_MDIO_O, ENET1_MDIO_T, ENET1_PTP_DELAY_REQ_RX, ENET1_PTP_DELAY_REQ_TX, ENET1_PTP_PDELAY_REQ_RX, ENET1_PTP_PDELAY_REQ_TX, ENET1_PTP_PDELAY_RESP_RX, ENET1_PTP_PDELAY_RESP_TX, ENET1_PTP_SYNC_FRAME_RX, ENET1_PTP_SYNC_FRAME_TX, ENET1_SOF_RX, ENET1_SOF_TX, ENET1_GMII_TXD, ENET1_GMII_COL, ENET1_GMII_CRS, ENET1_EXT_INTIN, ENET1_GMII_RX_CLK, ENET1_GMII_RX_DV, ENET1_GMII_RX_ER, ENET1_GMII_TX_CLK, ENET1_MDIO_I, ENET1_GMII_RXD, GPIO_I, GPIO_O, GPIO_T, I2C0_SDA_I, I2C0_SDA_O, I2C0_SDA_T, I2C0_SCL_I, I2C0_SCL_O, I2C0_SCL_T, I2C1_SDA_I, I2C1_SDA_O, I2C1_SDA_T, I2C1_SCL_I, I2C1_SCL_O, I2C1_SCL_T, PJTAG_TCK, PJTAG_TMS, PJTAG_TD_I, PJTAG_TD_T, PJTAG_TD_O, SDIO0_CLK, SDIO0_CLK_FB, SDIO0_CMD_O, SDIO0_CMD_I, SDIO0_CMD_T, SDIO0_DATA_I, SDIO0_DATA_O, SDIO0_DATA_T, SDIO0_LED, SDIO0_CDN, SDIO0_WP, SDIO0_BUSPOW, SDIO0_BUSVOLT, SDIO1_CLK, SDIO1_CLK_FB, SDIO1_CMD_O, SDIO1_CMD_I, SDIO1_CMD_T, SDIO1_DATA_I, SDIO1_DATA_O, SDIO1_DATA_T, SDIO1_LED, SDIO1_CDN, SDIO1_WP, SDIO1_BUSPOW, SDIO1_BUSVOLT, SPI0_SCLK_I, SPI0_SCLK_O, SPI0_SCLK_T, SPI0_MOSI_I, SPI0_MOSI_O, SPI0_MOSI_T, SPI0_MISO_I, SPI0_MISO_O, SPI0_MISO_T, SPI0_SS_I, SPI0_SS_O, SPI0_SS1_O, SPI0_SS2_O, SPI0_SS_T, SPI1_SCLK_I, SPI1_SCLK_O, SPI1_SCLK_T, SPI1_MOSI_I, SPI1_MOSI_O, SPI1_MOSI_T, SPI1_MISO_I, SPI1_MISO_O, SPI1_MISO_T, SPI1_SS_I, SPI1_SS_O, SPI1_SS1_O, SPI1_SS2_O, SPI1_SS_T, UART0_DTRN, UART0_RTSN, UART0_TX, UART0_CTSN, UART0_DCDN, UART0_DSRN, UART0_RIN, UART0_RX, UART1_DTRN, UART1_RTSN, UART1_TX, UART1_CTSN, UART1_DCDN, UART1_DSRN, UART1_RIN, UART1_RX, TTC0_WAVE0_OUT, TTC0_WAVE1_OUT, TTC0_WAVE2_OUT, TTC0_CLK0_IN, TTC0_CLK1_IN, TTC0_CLK2_IN, TTC1_WAVE0_OUT, TTC1_WAVE1_OUT, TTC1_WAVE2_OUT, TTC1_CLK0_IN, TTC1_CLK1_IN, TTC1_CLK2_IN, WDT_CLK_IN, WDT_RST_OUT, TRACE_CLK, TRACE_CTL, TRACE_DATA, USB0_PORT_INDCTL, USB1_PORT_INDCTL, USB0_VBUS_PWRSELECT, USB1_VBUS_PWRSELECT, USB0_VBUS_PWRFAULT, USB1_VBUS_PWRFAULT, SRAM_INTIN, M_AXI_GP0_ARVALID, M_AXI_GP0_AWVALID, M_AXI_GP0_BREADY, M_AXI_GP0_RREADY, M_AXI_GP0_WLAST, M_AXI_GP0_WVALID, M_AXI_GP0_ARID, M_AXI_GP0_AWID, M_AXI_GP0_WID, M_AXI_GP0_ARBURST, M_AXI_GP0_ARLOCK, M_AXI_GP0_ARSIZE, M_AXI_GP0_AWBURST, M_AXI_GP0_AWLOCK, M_AXI_GP0_AWSIZE, M_AXI_GP0_ARPROT, M_AXI_GP0_AWPROT, M_AXI_GP0_ARADDR, M_AXI_GP0_AWADDR, M_AXI_GP0_WDATA, M_AXI_GP0_ARCACHE, M_AXI_GP0_ARLEN, M_AXI_GP0_ARQOS, M_AXI_GP0_AWCACHE, M_AXI_GP0_AWLEN, M_AXI_GP0_AWQOS, M_AXI_GP0_WSTRB, M_AXI_GP0_ACLK, M_AXI_GP0_ARREADY, M_AXI_GP0_AWREADY, M_AXI_GP0_BVALID, M_AXI_GP0_RLAST, M_AXI_GP0_RVALID, M_AXI_GP0_WREADY, M_AXI_GP0_BID, M_AXI_GP0_RID, M_AXI_GP0_BRESP, M_AXI_GP0_RRESP, M_AXI_GP0_RDATA, M_AXI_GP1_ARVALID, M_AXI_GP1_AWVALID, M_AXI_GP1_BREADY, M_AXI_GP1_RREADY, M_AXI_GP1_WLAST, M_AXI_GP1_WVALID, M_AXI_GP1_ARID, M_AXI_GP1_AWID, M_AXI_GP1_WID, M_AXI_GP1_ARBURST, M_AXI_GP1_ARLOCK, M_AXI_GP1_ARSIZE, M_AXI_GP1_AWBURST, M_AXI_GP1_AWLOCK, M_AXI_GP1_AWSIZE, M_AXI_GP1_ARPROT, M_AXI_GP1_AWPROT, M_AXI_GP1_ARADDR, M_AXI_GP1_AWADDR, M_AXI_GP1_WDATA, M_AXI_GP1_ARCACHE, M_AXI_GP1_ARLEN, M_AXI_GP1_ARQOS, M_AXI_GP1_AWCACHE, M_AXI_GP1_AWLEN, M_AXI_GP1_AWQOS, M_AXI_GP1_WSTRB, M_AXI_GP1_ACLK, M_AXI_GP1_ARREADY, M_AXI_GP1_AWREADY, M_AXI_GP1_BVALID, M_AXI_GP1_RLAST, M_AXI_GP1_RVALID, M_AXI_GP1_WREADY, M_AXI_GP1_BID, M_AXI_GP1_RID, M_AXI_GP1_BRESP, M_AXI_GP1_RRESP, M_AXI_GP1_RDATA, S_AXI_GP0_ARREADY, S_AXI_GP0_AWREADY, S_AXI_GP0_BVALID, S_AXI_GP0_RLAST, S_AXI_GP0_RVALID, S_AXI_GP0_WREADY, S_AXI_GP0_BRESP, S_AXI_GP0_RRESP, S_AXI_GP0_RDATA, S_AXI_GP0_BID, S_AXI_GP0_RID, S_AXI_GP0_ACLK, S_AXI_GP0_ARVALID, S_AXI_GP0_AWVALID, S_AXI_GP0_BREADY, S_AXI_GP0_RREADY, S_AXI_GP0_WLAST, S_AXI_GP0_WVALID, S_AXI_GP0_ARBURST, S_AXI_GP0_ARLOCK, S_AXI_GP0_ARSIZE, S_AXI_GP0_AWBURST, S_AXI_GP0_AWLOCK, S_AXI_GP0_AWSIZE, S_AXI_GP0_ARPROT, S_AXI_GP0_AWPROT, S_AXI_GP0_ARADDR, S_AXI_GP0_AWADDR, S_AXI_GP0_WDATA, S_AXI_GP0_ARCACHE, S_AXI_GP0_ARLEN, S_AXI_GP0_ARQOS, S_AXI_GP0_AWCACHE, S_AXI_GP0_AWLEN, S_AXI_GP0_AWQOS, S_AXI_GP0_WSTRB, S_AXI_GP0_ARID, S_AXI_GP0_AWID, S_AXI_GP0_WID, S_AXI_GP1_ARREADY, S_AXI_GP1_AWREADY, S_AXI_GP1_BVALID, S_AXI_GP1_RLAST, S_AXI_GP1_RVALID, S_AXI_GP1_WREADY, S_AXI_GP1_BRESP, S_AXI_GP1_RRESP, S_AXI_GP1_RDATA, S_AXI_GP1_BID, S_AXI_GP1_RID, S_AXI_GP1_ACLK, S_AXI_GP1_ARVALID, S_AXI_GP1_AWVALID, S_AXI_GP1_BREADY, S_AXI_GP1_RREADY, S_AXI_GP1_WLAST, S_AXI_GP1_WVALID, S_AXI_GP1_ARBURST, S_AXI_GP1_ARLOCK, S_AXI_GP1_ARSIZE, S_AXI_GP1_AWBURST, S_AXI_GP1_AWLOCK, S_AXI_GP1_AWSIZE, S_AXI_GP1_ARPROT, S_AXI_GP1_AWPROT, S_AXI_GP1_ARADDR, S_AXI_GP1_AWADDR, S_AXI_GP1_WDATA, S_AXI_GP1_ARCACHE, S_AXI_GP1_ARLEN, S_AXI_GP1_ARQOS, S_AXI_GP1_AWCACHE, S_AXI_GP1_AWLEN, S_AXI_GP1_AWQOS, S_AXI_GP1_WSTRB, S_AXI_GP1_ARID, S_AXI_GP1_AWID, S_AXI_GP1_WID, S_AXI_ACP_AWREADY, S_AXI_ACP_ARREADY, S_AXI_ACP_BVALID, S_AXI_ACP_RLAST, S_AXI_ACP_RVALID, S_AXI_ACP_WREADY, S_AXI_ACP_BRESP, S_AXI_ACP_RRESP, S_AXI_ACP_BID, S_AXI_ACP_RID, S_AXI_ACP_RDATA, S_AXI_ACP_ACLK, S_AXI_ACP_ARVALID, S_AXI_ACP_AWVALID, S_AXI_ACP_BREADY, S_AXI_ACP_RREADY, S_AXI_ACP_WLAST, S_AXI_ACP_WVALID, S_AXI_ACP_ARID, S_AXI_ACP_ARPROT, S_AXI_ACP_AWID, S_AXI_ACP_AWPROT, S_AXI_ACP_WID, S_AXI_ACP_ARADDR, S_AXI_ACP_AWADDR, S_AXI_ACP_ARCACHE, S_AXI_ACP_ARLEN, S_AXI_ACP_ARQOS, S_AXI_ACP_AWCACHE, S_AXI_ACP_AWLEN, S_AXI_ACP_AWQOS, S_AXI_ACP_ARBURST, S_AXI_ACP_ARLOCK, S_AXI_ACP_ARSIZE, S_AXI_ACP_AWBURST, S_AXI_ACP_AWLOCK, S_AXI_ACP_AWSIZE, S_AXI_ACP_ARUSER, S_AXI_ACP_AWUSER, S_AXI_ACP_WDATA, S_AXI_ACP_WSTRB, S_AXI_HP0_ARREADY, S_AXI_HP0_AWREADY, S_AXI_HP0_BVALID, S_AXI_HP0_RLAST, S_AXI_HP0_RVALID, S_AXI_HP0_WREADY, S_AXI_HP0_BRESP, S_AXI_HP0_RRESP, S_AXI_HP0_BID, S_AXI_HP0_RID, S_AXI_HP0_RDATA, S_AXI_HP0_RCOUNT, S_AXI_HP0_WCOUNT, S_AXI_HP0_RACOUNT, S_AXI_HP0_WACOUNT, S_AXI_HP0_ACLK, S_AXI_HP0_ARVALID, S_AXI_HP0_AWVALID, S_AXI_HP0_BREADY, S_AXI_HP0_RDISSUECAP1_EN, S_AXI_HP0_RREADY, S_AXI_HP0_WLAST, S_AXI_HP0_WRISSUECAP1_EN, S_AXI_HP0_WVALID, S_AXI_HP0_ARBURST, S_AXI_HP0_ARLOCK, S_AXI_HP0_ARSIZE, S_AXI_HP0_AWBURST, S_AXI_HP0_AWLOCK, S_AXI_HP0_AWSIZE, S_AXI_HP0_ARPROT, S_AXI_HP0_AWPROT, S_AXI_HP0_ARADDR, S_AXI_HP0_AWADDR, S_AXI_HP0_ARCACHE, S_AXI_HP0_ARLEN, S_AXI_HP0_ARQOS, S_AXI_HP0_AWCACHE, S_AXI_HP0_AWLEN, S_AXI_HP0_AWQOS, S_AXI_HP0_ARID, S_AXI_HP0_AWID, S_AXI_HP0_WID, S_AXI_HP0_WDATA, S_AXI_HP0_WSTRB, S_AXI_HP1_ARREADY, S_AXI_HP1_AWREADY, S_AXI_HP1_BVALID, S_AXI_HP1_RLAST, S_AXI_HP1_RVALID, S_AXI_HP1_WREADY, S_AXI_HP1_BRESP, S_AXI_HP1_RRESP, S_AXI_HP1_BID, S_AXI_HP1_RID, S_AXI_HP1_RDATA, S_AXI_HP1_RCOUNT, S_AXI_HP1_WCOUNT, S_AXI_HP1_RACOUNT, S_AXI_HP1_WACOUNT, S_AXI_HP1_ACLK, S_AXI_HP1_ARVALID, S_AXI_HP1_AWVALID, S_AXI_HP1_BREADY, S_AXI_HP1_RDISSUECAP1_EN, S_AXI_HP1_RREADY, S_AXI_HP1_WLAST, S_AXI_HP1_WRISSUECAP1_EN, S_AXI_HP1_WVALID, S_AXI_HP1_ARBURST, S_AXI_HP1_ARLOCK, S_AXI_HP1_ARSIZE, S_AXI_HP1_AWBURST, S_AXI_HP1_AWLOCK, S_AXI_HP1_AWSIZE, S_AXI_HP1_ARPROT, S_AXI_HP1_AWPROT, S_AXI_HP1_ARADDR, S_AXI_HP1_AWADDR, S_AXI_HP1_ARCACHE, S_AXI_HP1_ARLEN, S_AXI_HP1_ARQOS, S_AXI_HP1_AWCACHE, S_AXI_HP1_AWLEN, S_AXI_HP1_AWQOS, S_AXI_HP1_ARID, S_AXI_HP1_AWID, S_AXI_HP1_WID, S_AXI_HP1_WDATA, S_AXI_HP1_WSTRB, S_AXI_HP2_ARREADY, S_AXI_HP2_AWREADY, S_AXI_HP2_BVALID, S_AXI_HP2_RLAST, S_AXI_HP2_RVALID, S_AXI_HP2_WREADY, S_AXI_HP2_BRESP, S_AXI_HP2_RRESP, S_AXI_HP2_BID, S_AXI_HP2_RID, S_AXI_HP2_RDATA, S_AXI_HP2_RCOUNT, S_AXI_HP2_WCOUNT, S_AXI_HP2_RACOUNT, S_AXI_HP2_WACOUNT, S_AXI_HP2_ACLK, S_AXI_HP2_ARVALID, S_AXI_HP2_AWVALID, S_AXI_HP2_BREADY, S_AXI_HP2_RDISSUECAP1_EN, S_AXI_HP2_RREADY, S_AXI_HP2_WLAST, S_AXI_HP2_WRISSUECAP1_EN, S_AXI_HP2_WVALID, S_AXI_HP2_ARBURST, S_AXI_HP2_ARLOCK, S_AXI_HP2_ARSIZE, S_AXI_HP2_AWBURST, S_AXI_HP2_AWLOCK, S_AXI_HP2_AWSIZE, S_AXI_HP2_ARPROT, S_AXI_HP2_AWPROT, S_AXI_HP2_ARADDR, S_AXI_HP2_AWADDR, S_AXI_HP2_ARCACHE, S_AXI_HP2_ARLEN, S_AXI_HP2_ARQOS, S_AXI_HP2_AWCACHE, S_AXI_HP2_AWLEN, S_AXI_HP2_AWQOS, S_AXI_HP2_ARID, S_AXI_HP2_AWID, S_AXI_HP2_WID, S_AXI_HP2_WDATA, S_AXI_HP2_WSTRB, S_AXI_HP3_ARREADY, S_AXI_HP3_AWREADY, S_AXI_HP3_BVALID, S_AXI_HP3_RLAST, S_AXI_HP3_RVALID, S_AXI_HP3_WREADY, S_AXI_HP3_BRESP, S_AXI_HP3_RRESP, S_AXI_HP3_BID, S_AXI_HP3_RID, S_AXI_HP3_RDATA, S_AXI_HP3_RCOUNT, S_AXI_HP3_WCOUNT, S_AXI_HP3_RACOUNT, S_AXI_HP3_WACOUNT, S_AXI_HP3_ACLK, S_AXI_HP3_ARVALID, S_AXI_HP3_AWVALID, S_AXI_HP3_BREADY, S_AXI_HP3_RDISSUECAP1_EN, S_AXI_HP3_RREADY, S_AXI_HP3_WLAST, S_AXI_HP3_WRISSUECAP1_EN, S_AXI_HP3_WVALID, S_AXI_HP3_ARBURST, S_AXI_HP3_ARLOCK, S_AXI_HP3_ARSIZE, S_AXI_HP3_AWBURST, S_AXI_HP3_AWLOCK, S_AXI_HP3_AWSIZE, S_AXI_HP3_ARPROT, S_AXI_HP3_AWPROT, S_AXI_HP3_ARADDR, S_AXI_HP3_AWADDR, S_AXI_HP3_ARCACHE, S_AXI_HP3_ARLEN, S_AXI_HP3_ARQOS, S_AXI_HP3_AWCACHE, S_AXI_HP3_AWLEN, S_AXI_HP3_AWQOS, S_AXI_HP3_ARID, S_AXI_HP3_AWID, S_AXI_HP3_WID, S_AXI_HP3_WDATA, S_AXI_HP3_WSTRB, DMA0_DATYPE, DMA0_DAVALID, DMA0_DRREADY, DMA0_ACLK, DMA0_DAREADY, DMA0_DRLAST, DMA0_DRVALID, DMA0_DRTYPE, DMA1_DATYPE, DMA1_DAVALID, DMA1_DRREADY, DMA1_ACLK, DMA1_DAREADY, DMA1_DRLAST, DMA1_DRVALID, DMA1_DRTYPE, DMA2_DATYPE, DMA2_DAVALID, DMA2_DRREADY, DMA2_ACLK, DMA2_DAREADY, DMA2_DRLAST, DMA2_DRVALID, DMA3_DRVALID, DMA3_DATYPE, DMA3_DAVALID, DMA3_DRREADY, DMA3_ACLK, DMA3_DAREADY, DMA3_DRLAST, DMA2_DRTYPE, DMA3_DRTYPE, FTMD_TRACEIN_DATA, FTMD_TRACEIN_VALID, FTMD_TRACEIN_CLK, FTMD_TRACEIN_ATID, FTMT_F2P_TRIG, FTMT_F2P_TRIGACK, FTMT_F2P_DEBUG, FTMT_P2F_TRIGACK, FTMT_P2F_TRIG, FTMT_P2F_DEBUG, FCLK_CLK3, FCLK_CLK2, FCLK_CLK1, FCLK_CLK0, FCLK_CLKTRIG3_N, FCLK_CLKTRIG2_N, FCLK_CLKTRIG1_N, FCLK_CLKTRIG0_N, FCLK_RESET3_N, FCLK_RESET2_N, FCLK_RESET1_N, FCLK_RESET0_N, FPGA_IDLE_N, DDR_ARB, IRQ_F2P, Core0_nFIQ, Core0_nIRQ, Core1_nFIQ, Core1_nIRQ, EVENT_EVENTO, EVENT_STANDBYWFE, EVENT_STANDBYWFI, EVENT_EVENTI, MIO, DDR_Clk, DDR_Clk_n, DDR_CKE, DDR_CS_n, DDR_RAS_n, DDR_CAS_n, DDR_WEB, DDR_BankAddr, DDR_Addr, DDR_ODT, DDR_DRSTB, DDR_DQ, DDR_DM, DDR_DQS, DDR_DQS_n, DDR_VRN, DDR_VRP, PS_SRSTB, PS_CLK, PS_PORB, IRQ_P2F_DMAC_ABORT, IRQ_P2F_DMAC0, IRQ_P2F_DMAC1, IRQ_P2F_DMAC2, IRQ_P2F_DMAC3, IRQ_P2F_DMAC4, IRQ_P2F_DMAC5, IRQ_P2F_DMAC6, IRQ_P2F_DMAC7, IRQ_P2F_SMC, IRQ_P2F_QSPI, IRQ_P2F_CTI, IRQ_P2F_GPIO, IRQ_P2F_USB0, IRQ_P2F_ENET0, IRQ_P2F_ENET_WAKE0, IRQ_P2F_SDIO0, IRQ_P2F_I2C0, IRQ_P2F_SPI0, IRQ_P2F_UART0, IRQ_P2F_CAN0, IRQ_P2F_USB1, IRQ_P2F_ENET1, IRQ_P2F_ENET_WAKE1, IRQ_P2F_SDIO1, IRQ_P2F_I2C1, IRQ_P2F_SPI1, IRQ_P2F_UART1, IRQ_P2F_CAN1) |

| DowngradeIPIdentifiedWarnings module | axi_vip_v1_1_8_top (parameter C_AXI_PROTOCOL=0, parameter C_AXI_INTERFACE_MODE=1, parameter integer C_AXI_ADDR_WIDTH=32, parameter integer C_AXI_WDATA_WIDTH=32, parameter integer C_AXI_RDATA_WIDTH=32, parameter integer C_AXI_WID_WIDTH=0, parameter integer C_AXI_RID_WIDTH=0, parameter integer C_AXI_AWUSER_WIDTH=0, parameter integer C_AXI_ARUSER_WIDTH=0, parameter integer C_AXI_WUSER_WIDTH=0, parameter integer C_AXI_RUSER_WIDTH=0, parameter integer C_AXI_BUSER_WIDTH=0, parameter integer C_AXI_SUPPORTS_NARROW=1, parameter integer C_AXI_HAS_BURST=1, parameter integer C_AXI_HAS_LOCK=1, parameter integer C_AXI_HAS_CACHE=1, parameter integer C_AXI_HAS_REGION=1, parameter integer C_AXI_HAS_PROT=1, parameter integer C_AXI_HAS_QOS=1, parameter integer C_AXI_HAS_WSTRB=1, parameter integer C_AXI_HAS_BRESP=1, parameter integer C_AXI_HAS_RRESP=1, parameter integer C_AXI_HAS_ARESETN=1)(input wire aclk |

| DowngradeIPIdentifiedWarnings module axi_vip_v1_1_8_top | ( | parameter | C_AXI_PROTOCOL = 0, |

| parameter | C_AXI_INTERFACE_MODE = 1, |

||

| parameter integer | C_AXI_ADDR_WIDTH = 32, |

||

| parameter integer | C_AXI_WDATA_WIDTH = 32, |

||

| parameter integer | C_AXI_RDATA_WIDTH = 32, |

||

| parameter integer | C_AXI_WID_WIDTH = 0, |

||

| parameter integer | C_AXI_RID_WIDTH = 0, |

||

| parameter integer | C_AXI_AWUSER_WIDTH = 0, |

||

| parameter integer | C_AXI_ARUSER_WIDTH = 0, |

||

| parameter integer | C_AXI_WUSER_WIDTH = 0, |

||

| parameter integer | C_AXI_RUSER_WIDTH = 0, |

||

| parameter integer | C_AXI_BUSER_WIDTH = 0, |

||

| parameter integer | C_AXI_SUPPORTS_NARROW = 1, |

||

| parameter integer | C_AXI_HAS_BURST = 1, |

||

| parameter integer | C_AXI_HAS_LOCK = 1, |

||

| parameter integer | C_AXI_HAS_CACHE = 1, |

||

| parameter integer | C_AXI_HAS_REGION = 1, |

||

| parameter integer | C_AXI_HAS_PROT = 1, |

||

| parameter integer | C_AXI_HAS_QOS = 1, |

||

| parameter integer | C_AXI_HAS_WSTRB = 1, |

||

| parameter integer | C_AXI_HAS_BRESP = 1, |

||

| parameter integer | C_AXI_HAS_RRESP = 1, |

||

| parameter integer | C_AXI_HAS_ARESETN = 1 |

||

| ) |

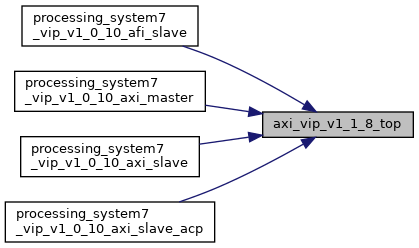

Referenced by processing_system7_vip_v1_0_10_afi_slave(), processing_system7_vip_v1_0_10_axi_master(), processing_system7_vip_v1_0_10_axi_slave(), and processing_system7_vip_v1_0_10_axi_slave_acp().

Definition at line 679 of file design_1_processing_system7_0_0.sv.

References DDR_Addr, DDR_BankAddr, DDR_CAS_n, DDR_CKE, DDR_Clk, DDR_Clk_n, DDR_CS_n, DDR_DM, DDR_DQ, DDR_DQS, DDR_DQS_n, DDR_DRSTB, DDR_ODT, DDR_RAS_n, DDR_VRN, DDR_VRP, DDR_WEB, ENET0_EXT_INTIN, ENET0_GMII_COL, ENET0_GMII_CRS, ENET0_GMII_RX_CLK, ENET0_GMII_RX_DV, ENET0_GMII_RX_ER, ENET0_GMII_RXD, ENET0_GMII_TX_CLK, ENET0_GMII_TX_EN, ENET0_GMII_TX_ER, ENET0_GMII_TXD, ENET0_MDIO_I, ENET0_MDIO_MDC, ENET0_MDIO_O, ENET0_MDIO_T, FCLK_CLK0, FCLK_CLK1, FCLK_CLK2, FCLK_CLK3, FCLK_RESET0_N, FCLK_RESET1_N, FCLK_RESET2_N, FCLK_RESET3_N, GPIO_I, GPIO_O, GPIO_T, IRQ_F2P, M_AXI_GP0_ACLK, M_AXI_GP0_ARADDR, M_AXI_GP0_ARBURST, M_AXI_GP0_ARCACHE, M_AXI_GP0_ARID, M_AXI_GP0_ARLEN, M_AXI_GP0_ARLOCK, M_AXI_GP0_ARPROT, M_AXI_GP0_ARQOS, M_AXI_GP0_ARREADY, M_AXI_GP0_ARSIZE, M_AXI_GP0_ARVALID, M_AXI_GP0_AWADDR, M_AXI_GP0_AWBURST, M_AXI_GP0_AWCACHE, M_AXI_GP0_AWID, M_AXI_GP0_AWLEN, M_AXI_GP0_AWLOCK, M_AXI_GP0_AWPROT, M_AXI_GP0_AWQOS, M_AXI_GP0_AWREADY, M_AXI_GP0_AWSIZE, M_AXI_GP0_AWVALID, M_AXI_GP0_BID, M_AXI_GP0_BREADY, M_AXI_GP0_BRESP, M_AXI_GP0_BVALID, M_AXI_GP0_RDATA, M_AXI_GP0_RID, M_AXI_GP0_RLAST, M_AXI_GP0_RREADY, M_AXI_GP0_RRESP, M_AXI_GP0_RVALID, M_AXI_GP0_WDATA, M_AXI_GP0_WID, M_AXI_GP0_WLAST, M_AXI_GP0_WREADY, M_AXI_GP0_WSTRB, M_AXI_GP0_WVALID, MIO, PS_CLK, PS_PORB, PS_SRSTB, S_AXI_HP0_ACLK, S_AXI_HP0_ARADDR, S_AXI_HP0_ARBURST, S_AXI_HP0_ARCACHE, S_AXI_HP0_ARID, S_AXI_HP0_ARLEN, S_AXI_HP0_ARLOCK, S_AXI_HP0_ARPROT, S_AXI_HP0_ARQOS, S_AXI_HP0_ARREADY, S_AXI_HP0_ARSIZE, S_AXI_HP0_ARVALID, S_AXI_HP0_AWADDR, S_AXI_HP0_AWBURST, S_AXI_HP0_AWCACHE, S_AXI_HP0_AWID, S_AXI_HP0_AWLEN, S_AXI_HP0_AWLOCK, S_AXI_HP0_AWPROT, S_AXI_HP0_AWQOS, S_AXI_HP0_AWREADY, S_AXI_HP0_AWSIZE, S_AXI_HP0_AWVALID, S_AXI_HP0_BID, S_AXI_HP0_BREADY, S_AXI_HP0_BRESP, S_AXI_HP0_BVALID, S_AXI_HP0_RACOUNT, S_AXI_HP0_RCOUNT, S_AXI_HP0_RDATA, S_AXI_HP0_RDISSUECAP1_EN, S_AXI_HP0_RID, S_AXI_HP0_RLAST, S_AXI_HP0_RREADY, S_AXI_HP0_RRESP, S_AXI_HP0_RVALID, S_AXI_HP0_WACOUNT, S_AXI_HP0_WCOUNT, S_AXI_HP0_WDATA, S_AXI_HP0_WID, S_AXI_HP0_WLAST, S_AXI_HP0_WREADY, S_AXI_HP0_WRISSUECAP1_EN, S_AXI_HP0_WSTRB, S_AXI_HP0_WVALID, TTC0_WAVE0_OUT, TTC0_WAVE1_OUT, and TTC0_WAVE2_OUT.

Definition at line 11860 of file processing_system7_vip_v1_0_vl_rfs.sv.

References CAN0_PHY_RX, CAN0_PHY_TX, CAN1_PHY_RX, CAN1_PHY_TX, Core0_nFIQ, Core0_nIRQ, Core1_nFIQ, Core1_nIRQ, DDR_Addr, DDR_ARB, DDR_BankAddr, DDR_CAS_n, DDR_CKE, DDR_Clk, DDR_Clk_n, DDR_CS_n, DDR_DM, DDR_DQ, DDR_DQS, DDR_DQS_n, DDR_DRSTB, DDR_ODT, DDR_RAS_n, DDR_VRN, DDR_VRP, DDR_WEB, DMA0_ACLK, DMA0_DAREADY, DMA0_DATYPE, DMA0_DAVALID, DMA0_DRLAST, DMA0_DRREADY, DMA0_DRTYPE, DMA0_DRVALID, DMA1_ACLK, DMA1_DAREADY, DMA1_DATYPE, DMA1_DAVALID, DMA1_DRLAST, DMA1_DRREADY, DMA1_DRTYPE, DMA1_DRVALID, DMA2_ACLK, DMA2_DAREADY, DMA2_DATYPE, DMA2_DAVALID, DMA2_DRLAST, DMA2_DRREADY, DMA2_DRTYPE, DMA2_DRVALID, DMA3_ACLK, DMA3_DAREADY, DMA3_DATYPE, DMA3_DAVALID, DMA3_DRLAST, DMA3_DRREADY, DMA3_DRTYPE, DMA3_DRVALID, ENET0_EXT_INTIN, ENET0_GMII_COL, ENET0_GMII_CRS, ENET0_GMII_RX_CLK, ENET0_GMII_RX_DV, ENET0_GMII_RX_ER, ENET0_GMII_RXD, ENET0_GMII_TX_CLK, ENET0_GMII_TX_EN, ENET0_GMII_TX_ER, ENET0_GMII_TXD, ENET0_MDIO_I, ENET0_MDIO_MDC, ENET0_MDIO_O, ENET0_MDIO_T, ENET0_PTP_DELAY_REQ_RX, ENET0_PTP_DELAY_REQ_TX, ENET0_PTP_PDELAY_REQ_RX, ENET0_PTP_PDELAY_REQ_TX, ENET0_PTP_PDELAY_RESP_RX, ENET0_PTP_PDELAY_RESP_TX, ENET0_PTP_SYNC_FRAME_RX, ENET0_PTP_SYNC_FRAME_TX, ENET0_SOF_RX, ENET0_SOF_TX, ENET1_EXT_INTIN, ENET1_GMII_COL, ENET1_GMII_CRS, ENET1_GMII_RX_CLK, ENET1_GMII_RX_DV, ENET1_GMII_RX_ER, ENET1_GMII_RXD, ENET1_GMII_TX_CLK, ENET1_GMII_TX_EN, ENET1_GMII_TX_ER, ENET1_GMII_TXD, ENET1_MDIO_I, ENET1_MDIO_MDC, ENET1_MDIO_O, ENET1_MDIO_T, ENET1_PTP_DELAY_REQ_RX, ENET1_PTP_DELAY_REQ_TX, ENET1_PTP_PDELAY_REQ_RX, ENET1_PTP_PDELAY_REQ_TX, ENET1_PTP_PDELAY_RESP_RX, ENET1_PTP_PDELAY_RESP_TX, ENET1_PTP_SYNC_FRAME_RX, ENET1_PTP_SYNC_FRAME_TX, ENET1_SOF_RX, ENET1_SOF_TX, EVENT_EVENTI, EVENT_EVENTO, EVENT_STANDBYWFE, EVENT_STANDBYWFI, FCLK_CLK0, FCLK_CLK1, FCLK_CLK2, FCLK_CLK3, FCLK_CLKTRIG0_N, FCLK_CLKTRIG1_N, FCLK_CLKTRIG2_N, FCLK_CLKTRIG3_N, FCLK_RESET0_N, FCLK_RESET1_N, FCLK_RESET2_N, FCLK_RESET3_N, FPGA_IDLE_N, FTMD_TRACEIN_ATID, FTMD_TRACEIN_CLK, FTMD_TRACEIN_DATA, FTMD_TRACEIN_VALID, FTMT_F2P_DEBUG, FTMT_P2F_DEBUG, GPIO_I, GPIO_O, GPIO_T, I2C0_SCL_I, I2C0_SCL_O, I2C0_SCL_T, I2C0_SDA_I, I2C0_SDA_O, I2C0_SDA_T, I2C1_SCL_I, I2C1_SCL_O, I2C1_SCL_T, I2C1_SDA_I, I2C1_SDA_O, I2C1_SDA_T, IRQ_F2P, IRQ_P2F_CAN0, IRQ_P2F_CAN1, IRQ_P2F_CTI, IRQ_P2F_DMAC0, IRQ_P2F_DMAC1, IRQ_P2F_DMAC2, IRQ_P2F_DMAC3, IRQ_P2F_DMAC4, IRQ_P2F_DMAC5, IRQ_P2F_DMAC6, IRQ_P2F_DMAC7, IRQ_P2F_DMAC_ABORT, IRQ_P2F_ENET0, IRQ_P2F_ENET1, IRQ_P2F_ENET_WAKE0, IRQ_P2F_ENET_WAKE1, IRQ_P2F_GPIO, IRQ_P2F_I2C0, IRQ_P2F_I2C1, IRQ_P2F_QSPI, IRQ_P2F_SDIO0, IRQ_P2F_SDIO1, IRQ_P2F_SMC, IRQ_P2F_SPI0, IRQ_P2F_SPI1, IRQ_P2F_UART0, IRQ_P2F_UART1, IRQ_P2F_USB0, IRQ_P2F_USB1, M_AXI_GP0_ACLK, M_AXI_GP0_ARADDR, M_AXI_GP0_ARBURST, M_AXI_GP0_ARCACHE, M_AXI_GP0_ARID, M_AXI_GP0_ARLEN, M_AXI_GP0_ARLOCK, M_AXI_GP0_ARPROT, M_AXI_GP0_ARQOS, M_AXI_GP0_ARREADY, M_AXI_GP0_ARSIZE, M_AXI_GP0_ARVALID, M_AXI_GP0_AWADDR, M_AXI_GP0_AWBURST, M_AXI_GP0_AWCACHE, M_AXI_GP0_AWID, M_AXI_GP0_AWLEN, M_AXI_GP0_AWLOCK, M_AXI_GP0_AWPROT, M_AXI_GP0_AWQOS, M_AXI_GP0_AWREADY, M_AXI_GP0_AWSIZE, M_AXI_GP0_AWVALID, M_AXI_GP0_BID, M_AXI_GP0_BREADY, M_AXI_GP0_BRESP, M_AXI_GP0_BVALID, M_AXI_GP0_RDATA, M_AXI_GP0_RID, M_AXI_GP0_RLAST, M_AXI_GP0_RREADY, M_AXI_GP0_RRESP, M_AXI_GP0_RVALID, M_AXI_GP0_WDATA, M_AXI_GP0_WID, M_AXI_GP0_WLAST, M_AXI_GP0_WREADY, M_AXI_GP0_WSTRB, M_AXI_GP0_WVALID, M_AXI_GP1_ACLK, M_AXI_GP1_ARADDR, M_AXI_GP1_ARBURST, M_AXI_GP1_ARCACHE, M_AXI_GP1_ARID, M_AXI_GP1_ARLEN, M_AXI_GP1_ARLOCK, M_AXI_GP1_ARPROT, M_AXI_GP1_ARQOS, M_AXI_GP1_ARREADY, M_AXI_GP1_ARSIZE, M_AXI_GP1_ARVALID, M_AXI_GP1_AWADDR, M_AXI_GP1_AWBURST, M_AXI_GP1_AWCACHE, M_AXI_GP1_AWID, M_AXI_GP1_AWLEN, M_AXI_GP1_AWLOCK, M_AXI_GP1_AWPROT, M_AXI_GP1_AWQOS, M_AXI_GP1_AWREADY, M_AXI_GP1_AWSIZE, M_AXI_GP1_AWVALID, M_AXI_GP1_BID, M_AXI_GP1_BREADY, M_AXI_GP1_BRESP, M_AXI_GP1_BVALID, M_AXI_GP1_RDATA, M_AXI_GP1_RID, M_AXI_GP1_RLAST, M_AXI_GP1_RREADY, M_AXI_GP1_RRESP, M_AXI_GP1_RVALID, M_AXI_GP1_WDATA, M_AXI_GP1_WID, M_AXI_GP1_WLAST, M_AXI_GP1_WREADY, M_AXI_GP1_WSTRB, M_AXI_GP1_WVALID, MIO, PJTAG_TCK, PJTAG_TMS, processing_system7_vip_v1_0_10_ddrc(), processing_system7_vip_v1_0_10_gen_reset(), processing_system7_vip_v1_0_10_interconnect_model(), processing_system7_vip_v1_0_10_ocmc(), processing_system7_vip_v1_0_10_regc(), PS_CLK, PS_PORB, PS_SRSTB, S_AXI_ACP_ACLK, S_AXI_ACP_ARADDR, S_AXI_ACP_ARBURST, S_AXI_ACP_ARCACHE, S_AXI_ACP_ARID, S_AXI_ACP_ARLEN, S_AXI_ACP_ARLOCK, S_AXI_ACP_ARPROT, S_AXI_ACP_ARQOS, S_AXI_ACP_ARREADY, S_AXI_ACP_ARSIZE, S_AXI_ACP_ARUSER, S_AXI_ACP_ARVALID, S_AXI_ACP_AWADDR, S_AXI_ACP_AWBURST, S_AXI_ACP_AWCACHE, S_AXI_ACP_AWID, S_AXI_ACP_AWLEN, S_AXI_ACP_AWLOCK, S_AXI_ACP_AWPROT, S_AXI_ACP_AWQOS, S_AXI_ACP_AWREADY, S_AXI_ACP_AWSIZE, S_AXI_ACP_AWUSER, S_AXI_ACP_AWVALID, S_AXI_ACP_BID, S_AXI_ACP_BREADY, S_AXI_ACP_BRESP, S_AXI_ACP_BVALID, S_AXI_ACP_RDATA, S_AXI_ACP_RID, S_AXI_ACP_RLAST, S_AXI_ACP_RREADY, S_AXI_ACP_RRESP, S_AXI_ACP_RVALID, S_AXI_ACP_WDATA, S_AXI_ACP_WID, S_AXI_ACP_WLAST, S_AXI_ACP_WREADY, S_AXI_ACP_WSTRB, S_AXI_ACP_WVALID, S_AXI_GP0_ACLK, S_AXI_GP0_ARADDR, S_AXI_GP0_ARBURST, S_AXI_GP0_ARCACHE, S_AXI_GP0_ARID, S_AXI_GP0_ARLEN, S_AXI_GP0_ARLOCK, S_AXI_GP0_ARPROT, S_AXI_GP0_ARQOS, S_AXI_GP0_ARREADY, S_AXI_GP0_ARSIZE, S_AXI_GP0_ARVALID, S_AXI_GP0_AWADDR, S_AXI_GP0_AWBURST, S_AXI_GP0_AWCACHE, S_AXI_GP0_AWID, S_AXI_GP0_AWLEN, S_AXI_GP0_AWLOCK, S_AXI_GP0_AWPROT, S_AXI_GP0_AWQOS, S_AXI_GP0_AWREADY, S_AXI_GP0_AWSIZE, S_AXI_GP0_AWVALID, S_AXI_GP0_BID, S_AXI_GP0_BREADY, S_AXI_GP0_BRESP, S_AXI_GP0_BVALID, S_AXI_GP0_RDATA, S_AXI_GP0_RID, S_AXI_GP0_RLAST, S_AXI_GP0_RREADY, S_AXI_GP0_RRESP, S_AXI_GP0_RVALID, S_AXI_GP0_WDATA, S_AXI_GP0_WID, S_AXI_GP0_WLAST, S_AXI_GP0_WREADY, S_AXI_GP0_WSTRB, S_AXI_GP0_WVALID, S_AXI_GP1_ACLK, S_AXI_GP1_ARADDR, S_AXI_GP1_ARBURST, S_AXI_GP1_ARCACHE, S_AXI_GP1_ARID, S_AXI_GP1_ARLEN, S_AXI_GP1_ARLOCK, S_AXI_GP1_ARPROT, S_AXI_GP1_ARQOS, S_AXI_GP1_ARREADY, S_AXI_GP1_ARSIZE, S_AXI_GP1_ARVALID, S_AXI_GP1_AWADDR, S_AXI_GP1_AWBURST, S_AXI_GP1_AWCACHE, S_AXI_GP1_AWID, S_AXI_GP1_AWLEN, S_AXI_GP1_AWLOCK, S_AXI_GP1_AWPROT, S_AXI_GP1_AWQOS, S_AXI_GP1_AWREADY, S_AXI_GP1_AWSIZE, S_AXI_GP1_AWVALID, S_AXI_GP1_BID, S_AXI_GP1_BREADY, S_AXI_GP1_BRESP, S_AXI_GP1_BVALID, S_AXI_GP1_RDATA, S_AXI_GP1_RID, S_AXI_GP1_RLAST, S_AXI_GP1_RREADY, S_AXI_GP1_RRESP, S_AXI_GP1_RVALID, S_AXI_GP1_WDATA, S_AXI_GP1_WID, S_AXI_GP1_WLAST, S_AXI_GP1_WREADY, S_AXI_GP1_WSTRB, S_AXI_GP1_WVALID, S_AXI_HP0_ACLK, S_AXI_HP0_ARADDR, S_AXI_HP0_ARBURST, S_AXI_HP0_ARCACHE, S_AXI_HP0_ARID, S_AXI_HP0_ARLEN, S_AXI_HP0_ARLOCK, S_AXI_HP0_ARPROT, S_AXI_HP0_ARQOS, S_AXI_HP0_ARREADY, S_AXI_HP0_ARSIZE, S_AXI_HP0_ARVALID, S_AXI_HP0_AWADDR, S_AXI_HP0_AWBURST, S_AXI_HP0_AWCACHE, S_AXI_HP0_AWID, S_AXI_HP0_AWLEN, S_AXI_HP0_AWLOCK, S_AXI_HP0_AWPROT, S_AXI_HP0_AWQOS, S_AXI_HP0_AWREADY, S_AXI_HP0_AWSIZE, S_AXI_HP0_AWVALID, S_AXI_HP0_BID, S_AXI_HP0_BREADY, S_AXI_HP0_BRESP, S_AXI_HP0_BVALID, S_AXI_HP0_RACOUNT, S_AXI_HP0_RCOUNT, S_AXI_HP0_RDATA, S_AXI_HP0_RDISSUECAP1_EN, S_AXI_HP0_RID, S_AXI_HP0_RLAST, S_AXI_HP0_RREADY, S_AXI_HP0_RRESP, S_AXI_HP0_RVALID, S_AXI_HP0_WACOUNT, S_AXI_HP0_WCOUNT, S_AXI_HP0_WDATA, S_AXI_HP0_WID, S_AXI_HP0_WLAST, S_AXI_HP0_WREADY, S_AXI_HP0_WRISSUECAP1_EN, S_AXI_HP0_WSTRB, S_AXI_HP0_WVALID, S_AXI_HP1_ACLK, S_AXI_HP1_ARADDR, S_AXI_HP1_ARBURST, S_AXI_HP1_ARCACHE, S_AXI_HP1_ARID, S_AXI_HP1_ARLEN, S_AXI_HP1_ARLOCK, S_AXI_HP1_ARPROT, S_AXI_HP1_ARQOS, S_AXI_HP1_ARREADY, S_AXI_HP1_ARSIZE, S_AXI_HP1_ARVALID, S_AXI_HP1_AWADDR, S_AXI_HP1_AWBURST, S_AXI_HP1_AWCACHE, S_AXI_HP1_AWID, S_AXI_HP1_AWLEN, S_AXI_HP1_AWLOCK, S_AXI_HP1_AWPROT, S_AXI_HP1_AWQOS, S_AXI_HP1_AWREADY, S_AXI_HP1_AWSIZE, S_AXI_HP1_AWVALID, S_AXI_HP1_BID, S_AXI_HP1_BREADY, S_AXI_HP1_BRESP, S_AXI_HP1_BVALID, S_AXI_HP1_RACOUNT, S_AXI_HP1_RCOUNT, S_AXI_HP1_RDATA, S_AXI_HP1_RDISSUECAP1_EN, S_AXI_HP1_RID, S_AXI_HP1_RLAST, S_AXI_HP1_RREADY, S_AXI_HP1_RRESP, S_AXI_HP1_RVALID, S_AXI_HP1_WACOUNT, S_AXI_HP1_WCOUNT, S_AXI_HP1_WDATA, S_AXI_HP1_WID, S_AXI_HP1_WLAST, S_AXI_HP1_WREADY, S_AXI_HP1_WRISSUECAP1_EN, S_AXI_HP1_WSTRB, S_AXI_HP1_WVALID, S_AXI_HP2_ACLK, S_AXI_HP2_ARADDR, S_AXI_HP2_ARBURST, S_AXI_HP2_ARCACHE, S_AXI_HP2_ARID, S_AXI_HP2_ARLEN, S_AXI_HP2_ARLOCK, S_AXI_HP2_ARPROT, S_AXI_HP2_ARQOS, S_AXI_HP2_ARREADY, S_AXI_HP2_ARSIZE, S_AXI_HP2_ARVALID, S_AXI_HP2_AWADDR, S_AXI_HP2_AWBURST, S_AXI_HP2_AWCACHE, S_AXI_HP2_AWID, S_AXI_HP2_AWLEN, S_AXI_HP2_AWLOCK, S_AXI_HP2_AWPROT, S_AXI_HP2_AWQOS, S_AXI_HP2_AWREADY, S_AXI_HP2_AWSIZE, S_AXI_HP2_AWVALID, S_AXI_HP2_BID, S_AXI_HP2_BREADY, S_AXI_HP2_BRESP, S_AXI_HP2_BVALID, S_AXI_HP2_RACOUNT, S_AXI_HP2_RCOUNT, S_AXI_HP2_RDATA, S_AXI_HP2_RDISSUECAP1_EN, S_AXI_HP2_RID, S_AXI_HP2_RLAST, S_AXI_HP2_RREADY, S_AXI_HP2_RRESP, S_AXI_HP2_RVALID, S_AXI_HP2_WACOUNT, S_AXI_HP2_WCOUNT, S_AXI_HP2_WDATA, S_AXI_HP2_WID, S_AXI_HP2_WLAST, S_AXI_HP2_WREADY, S_AXI_HP2_WRISSUECAP1_EN, S_AXI_HP2_WSTRB, S_AXI_HP2_WVALID, S_AXI_HP3_ACLK, S_AXI_HP3_ARADDR, S_AXI_HP3_ARBURST, S_AXI_HP3_ARCACHE, S_AXI_HP3_ARID, S_AXI_HP3_ARLEN, S_AXI_HP3_ARLOCK, S_AXI_HP3_ARPROT, S_AXI_HP3_ARQOS, S_AXI_HP3_ARREADY, S_AXI_HP3_ARSIZE, S_AXI_HP3_ARVALID, S_AXI_HP3_AWADDR, S_AXI_HP3_AWBURST, S_AXI_HP3_AWCACHE, S_AXI_HP3_AWID, S_AXI_HP3_AWLEN, S_AXI_HP3_AWLOCK, S_AXI_HP3_AWPROT, S_AXI_HP3_AWQOS, S_AXI_HP3_AWREADY, S_AXI_HP3_AWSIZE, S_AXI_HP3_AWVALID, S_AXI_HP3_BID, S_AXI_HP3_BREADY, S_AXI_HP3_BRESP, S_AXI_HP3_BVALID, S_AXI_HP3_RACOUNT, S_AXI_HP3_RCOUNT, S_AXI_HP3_RDATA, S_AXI_HP3_RDISSUECAP1_EN, S_AXI_HP3_RID, S_AXI_HP3_RLAST, S_AXI_HP3_RREADY, S_AXI_HP3_RRESP, S_AXI_HP3_RVALID, S_AXI_HP3_WACOUNT, S_AXI_HP3_WCOUNT, S_AXI_HP3_WDATA, S_AXI_HP3_WID, S_AXI_HP3_WLAST, S_AXI_HP3_WREADY, S_AXI_HP3_WRISSUECAP1_EN, S_AXI_HP3_WSTRB, S_AXI_HP3_WVALID, SDIO0_BUSPOW, SDIO0_BUSVOLT, SDIO0_CDN, SDIO0_CLK, SDIO0_CLK_FB, SDIO0_CMD_I, SDIO0_CMD_O, SDIO0_CMD_T, SDIO0_DATA_I, SDIO0_DATA_O, SDIO0_DATA_T, SDIO0_LED, SDIO0_WP, SDIO1_BUSPOW, SDIO1_BUSVOLT, SDIO1_CDN, SDIO1_CLK, SDIO1_CLK_FB, SDIO1_CMD_I, SDIO1_CMD_O, SDIO1_CMD_T, SDIO1_DATA_I, SDIO1_DATA_O, SDIO1_DATA_T, SDIO1_LED, SDIO1_WP, SPI0_MISO_I, SPI0_MISO_O, SPI0_MISO_T, SPI0_MOSI_I, SPI0_MOSI_O, SPI0_MOSI_T, SPI0_SCLK_I, SPI0_SCLK_O, SPI0_SCLK_T, SPI0_SS1_O, SPI0_SS2_O, SPI0_SS_I, SPI0_SS_O, SPI0_SS_T, SPI1_MISO_I, SPI1_MISO_O, SPI1_MISO_T, SPI1_MOSI_I, SPI1_MOSI_O, SPI1_MOSI_T, SPI1_SCLK_I, SPI1_SCLK_O, SPI1_SCLK_T, SPI1_SS1_O, SPI1_SS2_O, SPI1_SS_I, SPI1_SS_O, SPI1_SS_T, SRAM_INTIN, TRACE_CLK, TRACE_CTL, TRACE_DATA, TTC0_CLK0_IN, TTC0_CLK1_IN, TTC0_CLK2_IN, TTC0_WAVE0_OUT, TTC0_WAVE1_OUT, TTC0_WAVE2_OUT, TTC1_CLK0_IN, TTC1_CLK1_IN, TTC1_CLK2_IN, TTC1_WAVE0_OUT, TTC1_WAVE1_OUT, TTC1_WAVE2_OUT, UART0_CTSN, UART0_DCDN, UART0_DSRN, UART0_DTRN, UART0_RIN, UART0_RTSN, UART0_RX, UART0_TX, UART1_CTSN, UART1_DCDN, UART1_DSRN, UART1_DTRN, UART1_RIN, UART1_RTSN, UART1_RX, UART1_TX, USB0_PORT_INDCTL, USB0_VBUS_PWRFAULT, USB0_VBUS_PWRSELECT, USB1_PORT_INDCTL, USB1_VBUS_PWRFAULT, USB1_VBUS_PWRSELECT, WDT_CLK_IN, and WDT_RST_OUT.

| module processing_system7_vip_v1_0_10_afi_slave | ( | S_RESETN | , |

| S_ARREADY | , | ||

| S_AWREADY | , | ||

| S_BVALID | , | ||

| S_RLAST | , | ||

| S_RVALID | , | ||

| S_WREADY | , | ||

| S_BRESP | , | ||

| S_RRESP | , | ||

| S_RDATA | , | ||

| S_BID | , | ||

| S_RID | , | ||

| S_ACLK | , | ||

| S_ARVALID | , | ||

| S_AWVALID | , | ||

| S_BREADY | , | ||

| S_RREADY | , | ||

| S_WLAST | , | ||

| S_WVALID | , | ||

| S_ARBURST | , | ||

| S_ARLOCK | , | ||

| S_ARSIZE | , | ||

| S_AWBURST | , | ||

| S_AWLOCK | , | ||

| S_AWSIZE | , | ||

| S_ARPROT | , | ||

| S_AWPROT | , | ||

| S_ARADDR | , | ||

| S_AWADDR | , | ||

| S_WDATA | , | ||

| S_ARCACHE | , | ||

| S_ARLEN | , | ||

| S_AWCACHE | , | ||

| S_AWLEN | , | ||

| S_WSTRB | , | ||

| S_ARID | , | ||

| S_AWID | , | ||

| S_WID | , | ||

| S_AWQOS | , | ||

| S_ARQOS | , | ||

| SW_CLK | , | ||

| WR_DATA_ACK_OCM | , | ||

| WR_DATA_ACK_DDR | , | ||

| WR_ADDR | , | ||

| WR_DATA | , | ||

| WR_BYTES | , | ||

| WR_DATA_STRB | , | ||

| WR_DATA_VALID_OCM | , | ||

| WR_DATA_VALID_DDR | , | ||

| WR_QOS | , | ||

| RD_REQ_DDR | , | ||

| RD_REQ_OCM | , | ||

| RD_ADDR | , | ||

| RD_DATA_OCM | , | ||

| RD_DATA_DDR | , | ||

| RD_BYTES | , | ||

| RD_QOS | , | ||

| RD_DATA_VALID_OCM | , | ||

| RD_DATA_VALID_DDR | , | ||

| S_RDISSUECAP1_EN | , | ||

| S_WRISSUECAP1_EN | , | ||

| S_RCOUNT | , | ||

| S_WCOUNT | , | ||

| S_RACOUNT | , | ||

| S_WACOUNT | |||

| ) |

total valid bytes received in a complete burst transfer

total valid bytes received in a complete burst transfer

complete this

complete this

always

if else

always

if

else

always

aligned start address

get the data that is wrapped

aligned start address

get the strb that is wrapped

wrap type? then align the data

gives wrapped start address

gives wrapped start address

Store only AXI Burst Data ..

always

if(!ar_fifo_full)

if else

always*/

get the data that is wrapped

wrap begin

araddr[wr_rresp_cnt[int_rd_cntr_width-2:0]];

temp_dec == 2'b11) begin

else

always

Burst length

Data, addr, size, burst, len, RID, RRESP,valid_bytes

else

always

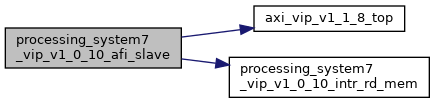

Definition at line 9948 of file processing_system7_vip_v1_0_vl_rfs.sv.

References aclken, aresetn, axi_vip_v1_1_8_top(), m_axi_araddr, m_axi_arburst, m_axi_arcache, m_axi_arid, m_axi_arlen, m_axi_arlock, m_axi_arprot, m_axi_arqos, m_axi_arready, m_axi_arregion, m_axi_arsize, m_axi_aruser, m_axi_arvalid, m_axi_awaddr, m_axi_awburst, m_axi_awcache, m_axi_awid, m_axi_awlen, m_axi_awlock, m_axi_awprot, m_axi_awqos, m_axi_awready, m_axi_awregion, m_axi_awsize, m_axi_awuser, m_axi_awvalid, m_axi_bid, m_axi_bready, m_axi_bresp, m_axi_buser, m_axi_bvalid, m_axi_rdata, m_axi_rid, m_axi_rlast, m_axi_rready, m_axi_rresp, m_axi_ruser, m_axi_rvalid, m_axi_wdata, m_axi_wid, m_axi_wlast, m_axi_wready, m_axi_wstrb, m_axi_wuser, m_axi_wvalid, processing_system7_vip_v1_0_10_intr_rd_mem(), s_axi_araddr, s_axi_arburst, s_axi_arcache, s_axi_arid, s_axi_arlen, s_axi_arlock, s_axi_arprot, s_axi_arqos, s_axi_arready, s_axi_arregion, s_axi_arsize, s_axi_aruser, s_axi_arvalid, s_axi_awaddr, s_axi_awburst, s_axi_awcache, s_axi_awid, s_axi_awlen, s_axi_awlock, s_axi_awprot, s_axi_awqos, s_axi_awready, s_axi_awregion, s_axi_awsize, s_axi_awuser, s_axi_awvalid, s_axi_bid, s_axi_bready, s_axi_bresp, s_axi_buser, s_axi_bvalid, s_axi_rdata, s_axi_rid, s_axi_rlast, s_axi_rready, s_axi_rresp, s_axi_ruser, s_axi_rvalid, s_axi_wdata, s_axi_wid, s_axi_wlast, s_axi_wready, s_axi_wstrb, s_axi_wuser, and s_axi_wvalid.

| module processing_system7_vip_v1_0_10_arb_hp0_1 | ( | sw_clk | , |

| rstn | , | ||

| w_qos_hp0 | , | ||

| r_qos_hp0 | , | ||

| w_qos_hp1 | , | ||

| r_qos_hp1 | , | ||

| wr_ack_ddr_hp0 | , | ||

| wr_data_hp0 | , | ||

| wr_strb_hp0 | , | ||

| wr_addr_hp0 | , | ||

| wr_bytes_hp0 | , | ||

| wr_dv_ddr_hp0 | , | ||

| rd_req_ddr_hp0 | , | ||

| rd_addr_hp0 | , | ||

| rd_bytes_hp0 | , | ||

| rd_data_ddr_hp0 | , | ||

| rd_dv_ddr_hp0 | , | ||

| wr_ack_ddr_hp1 | , | ||

| wr_data_hp1 | , | ||

| wr_strb_hp1 | , | ||

| wr_addr_hp1 | , | ||

| wr_bytes_hp1 | , | ||

| wr_dv_ddr_hp1 | , | ||

| rd_req_ddr_hp1 | , | ||

| rd_addr_hp1 | , | ||

| rd_bytes_hp1 | , | ||

| rd_data_ddr_hp1 | , | ||

| rd_dv_ddr_hp1 | , | ||

| ddr_wr_ack | , | ||

| ddr_wr_dv | , | ||

| ddr_rd_req | , | ||

| ddr_rd_dv | , | ||

| ddr_rd_qos | , | ||

| ddr_wr_qos | , | ||

| ddr_wr_addr | , | ||

| ddr_wr_data | , | ||

| ddr_wr_strb | , | ||

| ddr_wr_bytes | , | ||

| ddr_rd_addr | , | ||

| ddr_rd_data | , | ||

| ddr_rd_bytes | |||

| ) |

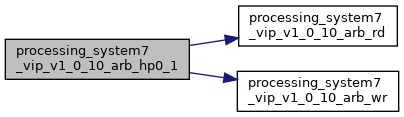

Definition at line 1135 of file processing_system7_vip_v1_0_vl_rfs.sv.

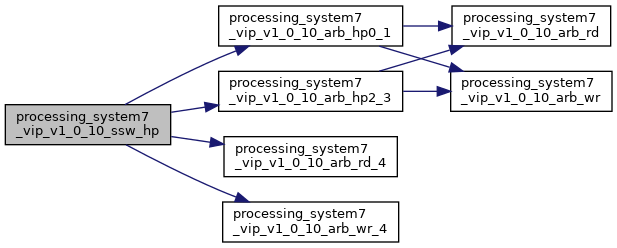

References processing_system7_vip_v1_0_10_arb_rd(), and processing_system7_vip_v1_0_10_arb_wr().

Referenced by processing_system7_vip_v1_0_10_ssw_hp().

| module processing_system7_vip_v1_0_10_arb_hp2_3 | ( | sw_clk | , |

| rstn | , | ||

| w_qos_hp2 | , | ||

| r_qos_hp2 | , | ||

| w_qos_hp3 | , | ||

| r_qos_hp3 | , | ||

| wr_ack_ddr_hp2 | , | ||

| wr_data_hp2 | , | ||

| wr_strb_hp2 | , | ||

| wr_addr_hp2 | , | ||

| wr_bytes_hp2 | , | ||

| wr_dv_ddr_hp2 | , | ||

| rd_req_ddr_hp2 | , | ||

| rd_addr_hp2 | , | ||

| rd_bytes_hp2 | , | ||

| rd_data_ddr_hp2 | , | ||

| rd_dv_ddr_hp2 | , | ||

| wr_ack_ddr_hp3 | , | ||

| wr_data_hp3 | , | ||

| wr_strb_hp3 | , | ||

| wr_addr_hp3 | , | ||

| wr_bytes_hp3 | , | ||

| wr_dv_ddr_hp3 | , | ||

| rd_req_ddr_hp3 | , | ||

| rd_addr_hp3 | , | ||

| rd_bytes_hp3 | , | ||

| rd_data_ddr_hp3 | , | ||

| rd_dv_ddr_hp3 | , | ||

| ddr_wr_ack | , | ||

| ddr_wr_dv | , | ||

| ddr_rd_req | , | ||

| ddr_rd_dv | , | ||

| ddr_rd_qos | , | ||

| ddr_wr_qos | , | ||

| ddr_wr_addr | , | ||

| ddr_wr_data | , | ||

| ddr_wr_strb | , | ||

| ddr_wr_bytes | , | ||

| ddr_rd_addr | , | ||

| ddr_rd_data | , | ||

| ddr_rd_bytes | |||

| ) |

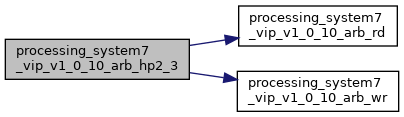

Definition at line 973 of file processing_system7_vip_v1_0_vl_rfs.sv.

References processing_system7_vip_v1_0_10_arb_rd(), and processing_system7_vip_v1_0_10_arb_wr().

Referenced by processing_system7_vip_v1_0_10_ssw_hp().

| module processing_system7_vip_v1_0_10_arb_rd | ( | rstn | , |

| sw_clk | , | ||

| qos1 | , | ||

| qos2 | , | ||

| prt_req1 | , | ||

| prt_req2 | , | ||

| prt_bytes1 | , | ||

| prt_bytes2 | , | ||

| prt_addr1 | , | ||

| prt_addr2 | , | ||

| prt_data1 | , | ||

| prt_data2 | , | ||

| prt_dv1 | , | ||

| prt_dv2 | , | ||

| prt_req | , | ||

| prt_qos | , | ||

| prt_addr | , | ||

| prt_bytes | , | ||

| prt_data | , | ||

| prt_dv | |||

| ) |

if else

always

Definition at line 203 of file processing_system7_vip_v1_0_vl_rfs.sv.

Referenced by processing_system7_vip_v1_0_10_arb_hp0_1(), processing_system7_vip_v1_0_10_arb_hp2_3(), processing_system7_vip_v1_0_10_fmsw_gp(), processing_system7_vip_v1_0_10_interconnect_model(), processing_system7_vip_v1_0_10_ocmc(), and processing_system7_vip_v1_0_10_regc().

| module processing_system7_vip_v1_0_10_arb_rd_4 | ( | rstn | , |

| sw_clk | , | ||

| qos1 | , | ||

| qos2 | , | ||

| qos3 | , | ||

| qos4 | , | ||

| prt_req1 | , | ||

| prt_req2 | , | ||

| prt_req3 | , | ||

| prt_req4 | , | ||

| prt_data1 | , | ||

| prt_data2 | , | ||

| prt_data3 | , | ||

| prt_data4 | , | ||

| prt_addr1 | , | ||

| prt_addr2 | , | ||

| prt_addr3 | , | ||

| prt_addr4 | , | ||

| prt_bytes1 | , | ||

| prt_bytes2 | , | ||

| prt_bytes3 | , | ||

| prt_bytes4 | , | ||

| prt_dv1 | , | ||

| prt_dv2 | , | ||

| prt_dv3 | , | ||

| prt_dv4 | , | ||

| prt_qos | , | ||

| prt_req | , | ||

| prt_data | , | ||

| prt_addr | , | ||

| prt_bytes | , | ||

| prt_dv | |||

| ) |

if else

always

Definition at line 716 of file processing_system7_vip_v1_0_vl_rfs.sv.

Referenced by processing_system7_vip_v1_0_10_ddrc(), and processing_system7_vip_v1_0_10_ssw_hp().

| module processing_system7_vip_v1_0_10_arb_wr | ( | rstn | , |

| sw_clk | , | ||

| qos1 | , | ||

| qos2 | , | ||

| prt_dv1 | , | ||

| prt_dv2 | , | ||

| prt_data1 | , | ||

| prt_data2 | , | ||

| prt_addr1 | , | ||

| prt_addr2 | , | ||

| prt_bytes1 | , | ||

| prt_bytes2 | , | ||

| prt_strb1 | , | ||

| prt_strb2 | , | ||

| prt_ack1 | , | ||

| prt_ack2 | , | ||

| prt_qos | , | ||

| prt_req | , | ||

| prt_data | , | ||

| prt_strb | , | ||

| prt_addr | , | ||

| prt_bytes | , | ||

| prt_ack | |||

| ) |

if else

always

Definition at line 11 of file processing_system7_vip_v1_0_vl_rfs.sv.

Referenced by processing_system7_vip_v1_0_10_arb_hp0_1(), processing_system7_vip_v1_0_10_arb_hp2_3(), processing_system7_vip_v1_0_10_fmsw_gp(), processing_system7_vip_v1_0_10_interconnect_model(), and processing_system7_vip_v1_0_10_ocmc().

| module processing_system7_vip_v1_0_10_arb_wr_4 | ( | rstn | , |

| sw_clk | , | ||

| qos1 | , | ||

| qos2 | , | ||

| qos3 | , | ||

| qos4 | , | ||

| prt_dv1 | , | ||

| prt_dv2 | , | ||

| prt_dv3 | , | ||

| prt_dv4 | , | ||

| prt_data1 | , | ||

| prt_data2 | , | ||

| prt_data3 | , | ||

| prt_data4 | , | ||

| prt_strb1 | , | ||

| prt_strb2 | , | ||

| prt_strb3 | , | ||

| prt_strb4 | , | ||

| prt_addr1 | , | ||

| prt_addr2 | , | ||

| prt_addr3 | , | ||

| prt_addr4 | , | ||

| prt_bytes1 | , | ||

| prt_bytes2 | , | ||

| prt_bytes3 | , | ||

| prt_bytes4 | , | ||

| prt_ack1 | , | ||

| prt_ack2 | , | ||

| prt_ack3 | , | ||

| prt_ack4 | , | ||

| prt_qos | , | ||

| prt_req | , | ||

| prt_data | , | ||

| prt_strb | , | ||

| prt_addr | , | ||

| prt_bytes | , | ||

| prt_ack | |||

| ) |

if else

always

Definition at line 360 of file processing_system7_vip_v1_0_vl_rfs.sv.

Referenced by processing_system7_vip_v1_0_10_ddrc(), and processing_system7_vip_v1_0_10_ssw_hp().

| module processing_system7_vip_v1_0_10_axi_master | ( | M_RESETN | , |

| M_ARVALID | , | ||

| M_AWVALID | , | ||

| M_BREADY | , | ||

| M_RREADY | , | ||

| M_WLAST | , | ||

| M_WVALID | , | ||

| M_ARID | , | ||

| M_AWID | , | ||

| M_WID | , | ||

| M_ARBURST | , | ||

| M_ARLOCK | , | ||

| M_ARSIZE | , | ||

| M_AWBURST | , | ||

| M_AWLOCK | , | ||

| M_AWSIZE | , | ||

| M_ARPROT | , | ||

| M_AWPROT | , | ||

| M_ARADDR | , | ||

| M_AWADDR | , | ||

| M_WDATA | , | ||

| M_ARCACHE | , | ||

| M_ARLEN | , | ||

| M_AWCACHE | , | ||

| M_AWLEN | , | ||

| M_ARQOS | , | ||

| M_AWQOS | , | ||

| M_WSTRB | , | ||

| M_ACLK | , | ||

| M_ARREADY | , | ||

| M_AWREADY | , | ||

| M_BVALID | , | ||

| M_RLAST | , | ||

| M_RVALID | , | ||

| M_WREADY | , | ||

| M_BID | , | ||

| M_RID | , | ||

| M_BRESP | , | ||

| M_RRESP | , | ||

| M_RDATA | |||

| ) |

get the data for 1 AXI burst transaction

write as 4 bytes (data_bus_width) ..

while

while

for unaligned address

while

for unaligned address

while

while

Definition at line 8417 of file processing_system7_vip_v1_0_vl_rfs.sv.

References aclken, aresetn, axi_vip_v1_1_8_top(), m_axi_araddr, m_axi_arburst, m_axi_arcache, m_axi_arid, m_axi_arlen, m_axi_arlock, m_axi_arprot, m_axi_arqos, m_axi_arready, m_axi_arregion, m_axi_arsize, m_axi_aruser, m_axi_arvalid, m_axi_awaddr, m_axi_awburst, m_axi_awcache, m_axi_awid, m_axi_awlen, m_axi_awlock, m_axi_awprot, m_axi_awqos, m_axi_awready, m_axi_awregion, m_axi_awsize, m_axi_awuser, m_axi_awvalid, m_axi_bid, m_axi_bready, m_axi_bresp, m_axi_buser, m_axi_bvalid, m_axi_rdata, m_axi_rid, m_axi_rlast, m_axi_rready, m_axi_rresp, m_axi_ruser, m_axi_rvalid, m_axi_wdata, m_axi_wid, m_axi_wlast, m_axi_wready, m_axi_wstrb, m_axi_wuser, m_axi_wvalid, s_axi_araddr, s_axi_arburst, s_axi_arcache, s_axi_arid, s_axi_arlen, s_axi_arlock, s_axi_arprot, s_axi_arqos, s_axi_arready, s_axi_arregion, s_axi_arsize, s_axi_aruser, s_axi_arvalid, s_axi_awaddr, s_axi_awburst, s_axi_awcache, s_axi_awid, s_axi_awlen, s_axi_awlock, s_axi_awprot, s_axi_awqos, s_axi_awready, s_axi_awregion, s_axi_awsize, s_axi_awuser, s_axi_awvalid, s_axi_bid, s_axi_bready, s_axi_bresp, s_axi_buser, s_axi_bvalid, s_axi_rdata, s_axi_rid, s_axi_rlast, s_axi_rready, s_axi_rresp, s_axi_ruser, s_axi_rvalid, s_axi_wdata, s_axi_wid, s_axi_wlast, s_axi_wready, s_axi_wstrb, s_axi_wuser, and s_axi_wvalid.

| module processing_system7_vip_v1_0_10_axi_slave | ( | S_RESETN | , |

| S_ARREADY | , | ||

| S_AWREADY | , | ||

| S_BVALID | , | ||

| S_RLAST | , | ||

| S_RVALID | , | ||

| S_WREADY | , | ||

| S_BRESP | , | ||

| S_RRESP | , | ||

| S_RDATA | , | ||

| S_BID | , | ||

| S_RID | , | ||

| S_ACLK | , | ||

| S_ARVALID | , | ||

| S_AWVALID | , | ||

| S_BREADY | , | ||

| S_RREADY | , | ||

| S_WLAST | , | ||

| S_WVALID | , | ||

| S_ARBURST | , | ||

| S_ARLOCK | , | ||

| S_ARSIZE | , | ||

| S_AWBURST | , | ||

| S_AWLOCK | , | ||

| S_AWSIZE | , | ||

| S_ARPROT | , | ||

| S_AWPROT | , | ||

| S_ARADDR | , | ||

| S_AWADDR | , | ||

| S_WDATA | , | ||

| S_ARCACHE | , | ||

| S_ARLEN | , | ||

| S_AWCACHE | , | ||

| S_AWLEN | , | ||

| S_WSTRB | , | ||

| S_ARID | , | ||

| S_AWID | , | ||

| S_WID | , | ||

| S_AWQOS | , | ||

| S_ARQOS | , | ||

| SW_CLK | , | ||

| WR_DATA_ACK_OCM | , | ||

| WR_DATA_ACK_DDR | , | ||

| WR_ADDR | , | ||

| WR_DATA | , | ||

| WR_DATA_STRB | , | ||

| WR_BYTES | , | ||

| WR_DATA_VALID_OCM | , | ||

| WR_DATA_VALID_DDR | , | ||

| WR_QOS | , | ||

| RD_QOS | , | ||

| RD_REQ_DDR | , | ||

| RD_REQ_OCM | , | ||

| RD_REQ_REG | , | ||

| RD_ADDR | , | ||

| RD_DATA_OCM | , | ||

| RD_DATA_DDR | , | ||

| RD_DATA_REG | , | ||

| RD_BYTES | , | ||

| RD_DATA_VALID_OCM | , | ||

| RD_DATA_VALID_DDR | , | ||

| RD_DATA_VALID_REG | |||

| ) |

total valid bytes received in a complete burst transfer

total valid bytes received in a complete burst transfer

complete this

complete this

always

if else

always

if

else

always

aligned start address

get the data that is wrapped

aligned start address

get the strb that is wrapped

wrap type? then align the data

gives wrapped start address

gives wrapped start address

Store only AXI Burst Data ..

always

if(!ar_fifo_full)

if else

always*/

get the data that is wrapped

wrap begin

araddr[wr_rresp_cnt[int_rd_cntr_width-2:0]];

temp_dec == 2'b11) begin

else

always

else

always

/ trr.data = new[((2**arsize[rd_cnt[int_rd_cntr_width-2:0]])*(arlen[rd_cnt[int_rd_cntr_width-2:0]]+1))];

Definition at line 5261 of file processing_system7_vip_v1_0_vl_rfs.sv.

References aclken, aresetn, axi_vip_v1_1_8_top(), m_axi_araddr, m_axi_arburst, m_axi_arcache, m_axi_arid, m_axi_arlen, m_axi_arlock, m_axi_arprot, m_axi_arqos, m_axi_arready, m_axi_arregion, m_axi_arsize, m_axi_aruser, m_axi_arvalid, m_axi_awaddr, m_axi_awburst, m_axi_awcache, m_axi_awid, m_axi_awlen, m_axi_awlock, m_axi_awprot, m_axi_awqos, m_axi_awready, m_axi_awregion, m_axi_awsize, m_axi_awuser, m_axi_awvalid, m_axi_bid, m_axi_bready, m_axi_bresp, m_axi_buser, m_axi_bvalid, m_axi_rdata, m_axi_rid, m_axi_rlast, m_axi_rready, m_axi_rresp, m_axi_ruser, m_axi_rvalid, m_axi_wdata, m_axi_wid, m_axi_wlast, m_axi_wready, m_axi_wstrb, m_axi_wuser, m_axi_wvalid, s_axi_araddr, s_axi_arburst, s_axi_arcache, s_axi_arid, s_axi_arlen, s_axi_arlock, s_axi_arprot, s_axi_arqos, s_axi_arready, s_axi_arregion, s_axi_arsize, s_axi_aruser, s_axi_arvalid, s_axi_awaddr, s_axi_awburst, s_axi_awcache, s_axi_awid, s_axi_awlen, s_axi_awlock, s_axi_awprot, s_axi_awqos, s_axi_awready, s_axi_awregion, s_axi_awsize, s_axi_awuser, s_axi_awvalid, s_axi_bid, s_axi_bready, s_axi_bresp, s_axi_buser, s_axi_bvalid, s_axi_rdata, s_axi_rid, s_axi_rlast, s_axi_rready, s_axi_rresp, s_axi_ruser, s_axi_rvalid, s_axi_wdata, s_axi_wid, s_axi_wlast, s_axi_wready, s_axi_wstrb, s_axi_wuser, and s_axi_wvalid.

| module processing_system7_vip_v1_0_10_axi_slave_acp | ( | S_RESETN | , |

| S_ARREADY | , | ||

| S_AWREADY | , | ||

| S_BVALID | , | ||

| S_RLAST | , | ||

| S_RVALID | , | ||

| S_WREADY | , | ||

| S_BRESP | , | ||

| S_RRESP | , | ||

| S_RDATA | , | ||

| S_BID | , | ||

| S_RID | , | ||

| S_ACLK | , | ||

| S_ARVALID | , | ||

| S_AWVALID | , | ||

| S_BREADY | , | ||

| S_RREADY | , | ||

| S_WLAST | , | ||

| S_WVALID | , | ||

| S_ARBURST | , | ||

| S_ARLOCK | , | ||

| S_ARSIZE | , | ||

| S_AWBURST | , | ||

| S_AWLOCK | , | ||

| S_AWSIZE | , | ||

| S_ARPROT | , | ||

| S_AWPROT | , | ||

| S_ARADDR | , | ||

| S_AWADDR | , | ||

| S_WDATA | , | ||

| S_ARCACHE | , | ||

| S_ARLEN | , | ||

| S_AWCACHE | , | ||

| S_AWLEN | , | ||

| S_WSTRB | , | ||

| S_ARID | , | ||

| S_AWID | , | ||

| S_WID | , | ||

| S_AWQOS | , | ||

| S_ARQOS | , | ||

| SW_CLK | , | ||

| WR_DATA_ACK_OCM | , | ||

| WR_DATA_ACK_DDR | , | ||

| WR_ADDR | , | ||

| WR_DATA | , | ||

| WR_DATA_STRB | , | ||

| WR_BYTES | , | ||

| WR_DATA_VALID_OCM | , | ||

| WR_DATA_VALID_DDR | , | ||

| WR_QOS | , | ||

| RD_QOS | , | ||

| RD_REQ_DDR | , | ||

| RD_REQ_OCM | , | ||

| RD_REQ_REG | , | ||

| RD_ADDR | , | ||

| RD_DATA_OCM | , | ||

| RD_DATA_DDR | , | ||

| RD_DATA_REG | , | ||

| RD_BYTES | , | ||

| RD_DATA_VALID_OCM | , | ||

| RD_DATA_VALID_DDR | , | ||

| RD_DATA_VALID_REG | |||

| ) |

total valid bytes received in a complete burst transfer

total valid bytes received in a complete burst transfer

complete this

complete this

always

if else

forever

always

if

else

forever

always

aligned start address

get the data that is wrapped

aligned start address

get the strb that is wrapped

wrap type? then align the data

gives wrapped start address

gives wrapped start address

Store only AXI Burst Data ..

always

if(!ar_fifo_full)

if else

forever

always*/

get the data that is wrapped

wrap begin

araddr[wr_rresp_cnt[int_rd_cntr_width-2:0]];

temp_dec == 2'b11) begin

else

always

else

always

Definition at line 6870 of file processing_system7_vip_v1_0_vl_rfs.sv.

References aclken, aresetn, axi_vip_v1_1_8_top(), m_axi_araddr, m_axi_arburst, m_axi_arcache, m_axi_arid, m_axi_arlen, m_axi_arlock, m_axi_arprot, m_axi_arqos, m_axi_arready, m_axi_arregion, m_axi_arsize, m_axi_aruser, m_axi_arvalid, m_axi_awaddr, m_axi_awburst, m_axi_awcache, m_axi_awid, m_axi_awlen, m_axi_awlock, m_axi_awprot, m_axi_awqos, m_axi_awready, m_axi_awregion, m_axi_awsize, m_axi_awuser, m_axi_awvalid, m_axi_bid, m_axi_bready, m_axi_bresp, m_axi_buser, m_axi_bvalid, m_axi_rdata, m_axi_rid, m_axi_rlast, m_axi_rready, m_axi_rresp, m_axi_ruser, m_axi_rvalid, m_axi_wdata, m_axi_wid, m_axi_wlast, m_axi_wready, m_axi_wstrb, m_axi_wuser, m_axi_wvalid, s_axi_araddr, s_axi_arburst, s_axi_arcache, s_axi_arid, s_axi_arlen, s_axi_arlock, s_axi_arprot, s_axi_arqos, s_axi_arready, s_axi_arregion, s_axi_arsize, s_axi_aruser, s_axi_arvalid, s_axi_awaddr, s_axi_awburst, s_axi_awcache, s_axi_awid, s_axi_awlen, s_axi_awlock, s_axi_awprot, s_axi_awqos, s_axi_awready, s_axi_awregion, s_axi_awsize, s_axi_awuser, s_axi_awvalid, s_axi_bid, s_axi_bready, s_axi_bresp, s_axi_buser, s_axi_bvalid, s_axi_rdata, s_axi_rid, s_axi_rlast, s_axi_rready, s_axi_rresp, s_axi_ruser, s_axi_rvalid, s_axi_wdata, s_axi_wid, s_axi_wlast, s_axi_wready, s_axi_wstrb, s_axi_wuser, and s_axi_wvalid.

| module processing_system7_vip_v1_0_10_ddrc | ( | rstn | , |

| sw_clk | , | ||

| ddr_wr_ack_port0 | , | ||

| ddr_wr_dv_port0 | , | ||

| ddr_rd_req_port0 | , | ||

| ddr_rd_dv_port0 | , | ||

| ddr_wr_addr_port0 | , | ||

| ddr_wr_data_port0 | , | ||

| ddr_wr_strb_port0 | , | ||

| ddr_wr_bytes_port0 | , | ||

| ddr_rd_addr_port0 | , | ||

| ddr_rd_data_port0 | , | ||

| ddr_rd_bytes_port0 | , | ||

| ddr_wr_qos_port0 | , | ||

| ddr_rd_qos_port0 | , | ||

| ddr_wr_ack_port1 | , | ||

| ddr_wr_dv_port1 | , | ||

| ddr_rd_req_port1 | , | ||

| ddr_rd_dv_port1 | , | ||

| ddr_wr_addr_port1 | , | ||

| ddr_wr_data_port1 | , | ||

| ddr_wr_strb_port1 | , | ||

| ddr_wr_bytes_port1 | , | ||

| ddr_rd_addr_port1 | , | ||

| ddr_rd_data_port1 | , | ||

| ddr_rd_bytes_port1 | , | ||

| ddr_wr_qos_port1 | , | ||

| ddr_rd_qos_port1 | , | ||

| ddr_wr_ack_port2 | , | ||

| ddr_wr_dv_port2 | , | ||

| ddr_rd_req_port2 | , | ||

| ddr_rd_dv_port2 | , | ||

| ddr_wr_addr_port2 | , | ||

| ddr_wr_data_port2 | , | ||

| ddr_wr_strb_port2 | , | ||

| ddr_wr_bytes_port2 | , | ||

| ddr_rd_addr_port2 | , | ||

| ddr_rd_data_port2 | , | ||

| ddr_rd_bytes_port2 | , | ||

| ddr_wr_qos_port2 | , | ||

| ddr_rd_qos_port2 | , | ||

| ddr_wr_ack_port3 | , | ||

| ddr_wr_dv_port3 | , | ||

| ddr_rd_req_port3 | , | ||

| ddr_rd_dv_port3 | , | ||

| ddr_wr_addr_port3 | , | ||

| ddr_wr_data_port3 | , | ||

| ddr_wr_strb_port3 | , | ||

| ddr_wr_bytes_port3 | , | ||

| ddr_rd_addr_port3 | , | ||

| ddr_rd_data_port3 | , | ||

| ddr_rd_bytes_port3 | , | ||

| ddr_wr_qos_port3 | , | ||

| ddr_rd_qos_port3 | |||

| ) |

if

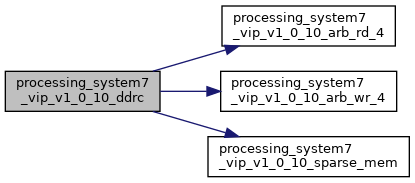

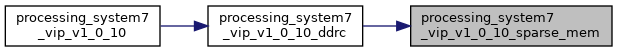

Definition at line 4934 of file processing_system7_vip_v1_0_vl_rfs.sv.

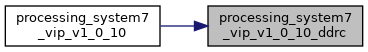

References processing_system7_vip_v1_0_10_arb_rd_4(), processing_system7_vip_v1_0_10_arb_wr_4(), and processing_system7_vip_v1_0_10_sparse_mem().

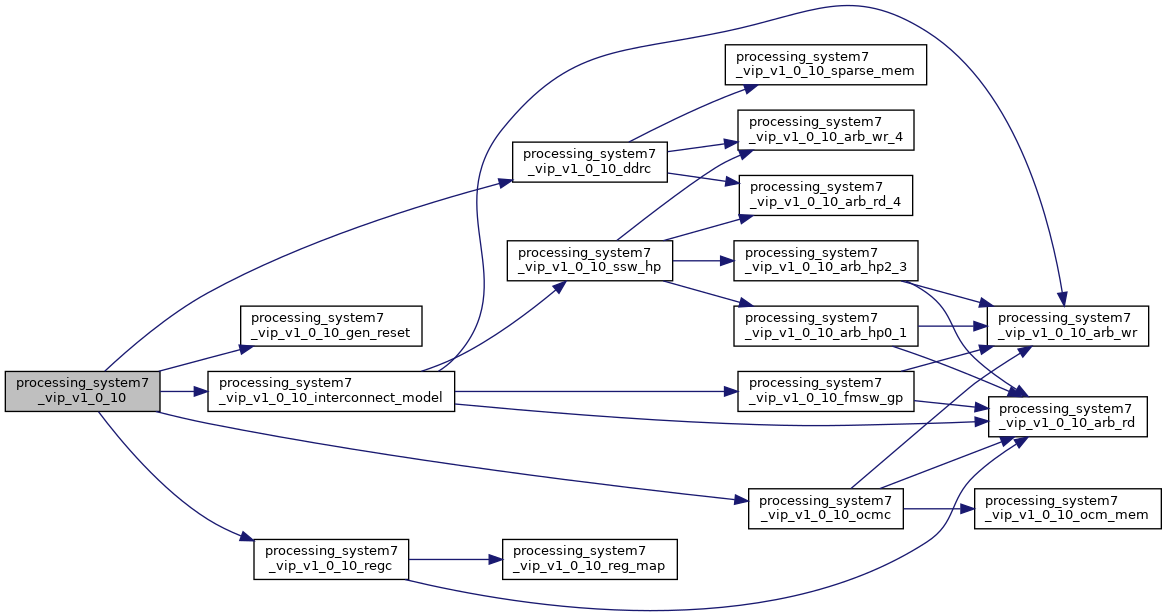

Referenced by processing_system7_vip_v1_0_10().

| module processing_system7_vip_v1_0_10_fmsw_gp | ( | sw_clk | , |

| rstn | , | ||

| w_qos_gp0 | , | ||

| r_qos_gp0 | , | ||

| wr_ack_ocm_gp0 | , | ||

| wr_ack_ddr_gp0 | , | ||

| wr_data_gp0 | , | ||

| wr_strb_gp0 | , | ||

| wr_addr_gp0 | , | ||

| wr_bytes_gp0 | , | ||

| wr_dv_ocm_gp0 | , | ||

| wr_dv_ddr_gp0 | , | ||

| rd_req_ocm_gp0 | , | ||

| rd_req_ddr_gp0 | , | ||

| rd_req_reg_gp0 | , | ||

| rd_addr_gp0 | , | ||

| rd_bytes_gp0 | , | ||

| rd_data_ocm_gp0 | , | ||

| rd_data_ddr_gp0 | , | ||

| rd_data_reg_gp0 | , | ||

| rd_dv_ocm_gp0 | , | ||

| rd_dv_ddr_gp0 | , | ||

| rd_dv_reg_gp0 | , | ||

| w_qos_gp1 | , | ||

| r_qos_gp1 | , | ||

| wr_ack_ocm_gp1 | , | ||

| wr_ack_ddr_gp1 | , | ||

| wr_data_gp1 | , | ||

| wr_strb_gp1 | , | ||

| wr_addr_gp1 | , | ||

| wr_bytes_gp1 | , | ||

| wr_dv_ocm_gp1 | , | ||

| wr_dv_ddr_gp1 | , | ||

| rd_req_ocm_gp1 | , | ||

| rd_req_ddr_gp1 | , | ||

| rd_req_reg_gp1 | , | ||

| rd_addr_gp1 | , | ||

| rd_bytes_gp1 | , | ||

| rd_data_ocm_gp1 | , | ||

| rd_data_ddr_gp1 | , | ||

| rd_data_reg_gp1 | , | ||

| rd_dv_ocm_gp1 | , | ||

| rd_dv_ddr_gp1 | , | ||

| rd_dv_reg_gp1 | , | ||

| ocm_wr_ack | , | ||

| ocm_wr_dv | , | ||

| ocm_rd_req | , | ||

| ocm_rd_dv | , | ||

| ddr_wr_ack | , | ||

| ddr_wr_dv | , | ||

| ddr_rd_req | , | ||

| ddr_rd_dv | , | ||

| reg_rd_req | , | ||

| reg_rd_dv | , | ||

| ocm_wr_qos | , | ||

| ddr_wr_qos | , | ||

| ocm_rd_qos | , | ||

| ddr_rd_qos | , | ||

| reg_rd_qos | , | ||

| ocm_wr_addr | , | ||

| ocm_wr_data | , | ||

| ocm_wr_strb | , | ||

| ocm_wr_bytes | , | ||

| ocm_rd_addr | , | ||

| ocm_rd_data | , | ||

| ocm_rd_bytes | , | ||

| ddr_wr_addr | , | ||

| ddr_wr_data | , | ||

| ddr_wr_strb | , | ||

| ddr_wr_bytes | , | ||

| ddr_rd_addr | , | ||

| ddr_rd_data | , | ||

| ddr_rd_bytes | , | ||

| reg_rd_addr | , | ||

| reg_rd_data | , | ||

| reg_rd_bytes | |||

| ) |

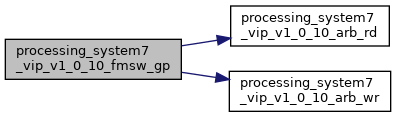

Definition at line 3300 of file processing_system7_vip_v1_0_vl_rfs.sv.

References processing_system7_vip_v1_0_10_arb_rd(), and processing_system7_vip_v1_0_10_arb_wr().

Referenced by processing_system7_vip_v1_0_10_interconnect_model().

| module processing_system7_vip_v1_0_10_gen_clock | ( | ps_clk | , |

| sw_clk | , | ||

| fclk_clk3 | , | ||

| fclk_clk2 | , | ||

| fclk_clk1 | , | ||

| fclk_clk0 | |||

| ) |

Definition at line 4874 of file processing_system7_vip_v1_0_vl_rfs.sv.

| module processing_system7_vip_v1_0_10_gen_reset | ( | por_rst_n | , |

| sys_rst_n | , | ||

| rst_out_n | , | ||

| m_axi_gp0_clk | , | ||

| m_axi_gp1_clk | , | ||

| s_axi_gp0_clk | , | ||

| s_axi_gp1_clk | , | ||

| s_axi_hp0_clk | , | ||

| s_axi_hp1_clk | , | ||

| s_axi_hp2_clk | , | ||

| s_axi_hp3_clk | , | ||

| s_axi_acp_clk | , | ||

| m_axi_gp0_rstn | , | ||

| m_axi_gp1_rstn | , | ||

| s_axi_gp0_rstn | , | ||

| s_axi_gp1_rstn | , | ||

| s_axi_hp0_rstn | , | ||

| s_axi_hp1_rstn | , | ||

| s_axi_hp2_rstn | , | ||

| s_axi_hp3_rstn | , | ||

| s_axi_acp_rstn | , | ||

| fclk_reset3_n | , | ||

| fclk_reset2_n | , | ||

| fclk_reset1_n | , | ||

| fclk_reset0_n | , | ||

| fpga_acp_reset_n | , | ||

| fpga_gp_m0_reset_n | , | ||

| fpga_gp_m1_reset_n | , | ||

| fpga_gp_s0_reset_n | , | ||

| fpga_gp_s1_reset_n | , | ||

| fpga_hp_s0_reset_n | , | ||

| fpga_hp_s1_reset_n | , | ||

| fpga_hp_s2_reset_n | , | ||

| fpga_hp_s3_reset_n | |||

| ) |

Definition at line 4638 of file processing_system7_vip_v1_0_vl_rfs.sv.

Referenced by processing_system7_vip_v1_0_10().

| module processing_system7_vip_v1_0_10_interconnect_model | ( | rstn | , |

| sw_clk | , | ||

| w_qos_gp0 | , | ||

| w_qos_gp1 | , | ||

| w_qos_hp0 | , | ||

| w_qos_hp1 | , | ||

| w_qos_hp2 | , | ||

| w_qos_hp3 | , | ||

| r_qos_gp0 | , | ||

| r_qos_gp1 | , | ||

| r_qos_hp0 | , | ||

| r_qos_hp1 | , | ||

| r_qos_hp2 | , | ||

| r_qos_hp3 | , | ||

| wr_ack_ddr_gp0 | , | ||

| wr_ack_ocm_gp0 | , | ||

| wr_data_gp0 | , | ||

| wr_strb_gp0 | , | ||

| wr_addr_gp0 | , | ||

| wr_bytes_gp0 | , | ||

| wr_dv_ddr_gp0 | , | ||

| wr_dv_ocm_gp0 | , | ||

| rd_req_ddr_gp0 | , | ||

| rd_req_ocm_gp0 | , | ||

| rd_req_reg_gp0 | , | ||

| rd_addr_gp0 | , | ||

| rd_bytes_gp0 | , | ||

| rd_data_ddr_gp0 | , | ||

| rd_data_ocm_gp0 | , | ||

| rd_data_reg_gp0 | , | ||

| rd_dv_ddr_gp0 | , | ||

| rd_dv_ocm_gp0 | , | ||

| rd_dv_reg_gp0 | , | ||

| wr_ack_ddr_gp1 | , | ||

| wr_ack_ocm_gp1 | , | ||

| wr_data_gp1 | , | ||

| wr_strb_gp1 | , | ||

| wr_addr_gp1 | , | ||

| wr_bytes_gp1 | , | ||

| wr_dv_ddr_gp1 | , | ||

| wr_dv_ocm_gp1 | , | ||

| rd_req_ddr_gp1 | , | ||

| rd_req_ocm_gp1 | , | ||

| rd_req_reg_gp1 | , | ||

| rd_addr_gp1 | , | ||

| rd_bytes_gp1 | , | ||

| rd_data_ddr_gp1 | , | ||

| rd_data_ocm_gp1 | , | ||

| rd_data_reg_gp1 | , | ||

| rd_dv_ddr_gp1 | , | ||

| rd_dv_ocm_gp1 | , | ||

| rd_dv_reg_gp1 | , | ||

| wr_ack_ddr_hp0 | , | ||

| wr_ack_ocm_hp0 | , | ||

| wr_data_hp0 | , | ||

| wr_strb_hp0 | , | ||

| wr_addr_hp0 | , | ||

| wr_bytes_hp0 | , | ||

| wr_dv_ddr_hp0 | , | ||

| wr_dv_ocm_hp0 | , | ||

| rd_req_ddr_hp0 | , | ||

| rd_req_ocm_hp0 | , | ||

| rd_addr_hp0 | , | ||

| rd_bytes_hp0 | , | ||

| rd_data_ddr_hp0 | , | ||

| rd_data_ocm_hp0 | , | ||

| rd_dv_ddr_hp0 | , | ||

| rd_dv_ocm_hp0 | , | ||

| wr_ack_ddr_hp1 | , | ||

| wr_ack_ocm_hp1 | , | ||

| wr_data_hp1 | , | ||

| wr_strb_hp1 | , | ||

| wr_addr_hp1 | , | ||

| wr_bytes_hp1 | , | ||

| wr_dv_ddr_hp1 | , | ||

| wr_dv_ocm_hp1 | , | ||

| rd_req_ddr_hp1 | , | ||

| rd_req_ocm_hp1 | , | ||

| rd_addr_hp1 | , | ||

| rd_bytes_hp1 | , | ||

| rd_data_ddr_hp1 | , | ||

| rd_data_ocm_hp1 | , | ||

| rd_dv_ddr_hp1 | , | ||

| rd_dv_ocm_hp1 | , | ||

| wr_ack_ddr_hp2 | , | ||

| wr_ack_ocm_hp2 | , | ||

| wr_data_hp2 | , | ||

| wr_strb_hp2 | , | ||

| wr_addr_hp2 | , | ||

| wr_bytes_hp2 | , | ||

| wr_dv_ddr_hp2 | , | ||

| wr_dv_ocm_hp2 | , | ||

| rd_req_ddr_hp2 | , | ||

| rd_req_ocm_hp2 | , | ||

| rd_addr_hp2 | , | ||

| rd_bytes_hp2 | , | ||

| rd_data_ddr_hp2 | , | ||

| rd_data_ocm_hp2 | , | ||

| rd_dv_ddr_hp2 | , | ||

| rd_dv_ocm_hp2 | , | ||

| wr_ack_ddr_hp3 | , | ||

| wr_ack_ocm_hp3 | , | ||

| wr_data_hp3 | , | ||

| wr_strb_hp3 | , | ||

| wr_addr_hp3 | , | ||

| wr_bytes_hp3 | , | ||

| wr_dv_ddr_hp3 | , | ||

| wr_dv_ocm_hp3 | , | ||

| rd_req_ddr_hp3 | , | ||

| rd_req_ocm_hp3 | , | ||

| rd_addr_hp3 | , | ||

| rd_bytes_hp3 | , | ||

| rd_data_ddr_hp3 | , | ||

| rd_data_ocm_hp3 | , | ||

| rd_dv_ddr_hp3 | , | ||

| rd_dv_ocm_hp3 | , | ||

| ddr_wr_ack_port1 | , | ||

| ddr_wr_dv_port1 | , | ||

| ddr_rd_req_port1 | , | ||

| ddr_rd_dv_port1 | , | ||

| ddr_wr_addr_port1 | , | ||

| ddr_wr_data_port1 | , | ||

| ddr_wr_strb_port1 | , | ||

| ddr_wr_bytes_port1 | , | ||

| ddr_rd_addr_port1 | , | ||

| ddr_rd_data_port1 | , | ||

| ddr_rd_bytes_port1 | , | ||

| ddr_wr_qos_port1 | , | ||

| ddr_rd_qos_port1 | , | ||

| ddr_wr_ack_port2 | , | ||

| ddr_wr_dv_port2 | , | ||

| ddr_rd_req_port2 | , | ||

| ddr_rd_dv_port2 | , | ||

| ddr_wr_addr_port2 | , | ||

| ddr_wr_data_port2 | , | ||

| ddr_wr_strb_port2 | , | ||

| ddr_wr_bytes_port2 | , | ||

| ddr_rd_addr_port2 | , | ||

| ddr_rd_data_port2 | , | ||

| ddr_rd_bytes_port2 | , | ||

| ddr_wr_qos_port2 | , | ||

| ddr_rd_qos_port2 | , | ||

| ddr_wr_ack_port3 | , | ||

| ddr_wr_dv_port3 | , | ||

| ddr_rd_req_port3 | , | ||

| ddr_rd_dv_port3 | , | ||

| ddr_wr_addr_port3 | , | ||

| ddr_wr_data_port3 | , | ||

| ddr_wr_strb_port3 | , | ||

| ddr_wr_bytes_port3 | , | ||

| ddr_rd_addr_port3 | , | ||

| ddr_rd_data_port3 | , | ||

| ddr_rd_bytes_port3 | , | ||

| ddr_wr_qos_port3 | , | ||

| ddr_rd_qos_port3 | , | ||

| ocm_wr_qos_port1 | , | ||

| ocm_rd_qos_port1 | , | ||

| ocm_wr_dv_port1 | , | ||

| ocm_wr_data_port1 | , | ||

| ocm_wr_strb_port1 | , | ||

| ocm_wr_addr_port1 | , | ||

| ocm_wr_bytes_port1 | , | ||

| ocm_wr_ack_port1 | , | ||

| ocm_rd_req_port1 | , | ||

| ocm_rd_data_port1 | , | ||

| ocm_rd_addr_port1 | , | ||

| ocm_rd_bytes_port1 | , | ||

| ocm_rd_dv_port1 | , | ||

| reg_rd_qos_port1 | , | ||

| reg_rd_req_port1 | , | ||

| reg_rd_data_port1 | , | ||

| reg_rd_addr_port1 | , | ||

| reg_rd_bytes_port1 | , | ||

| reg_rd_dv_port1 | |||

| ) |

chk

chk

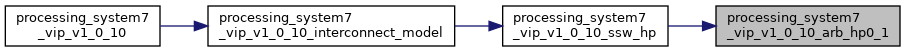

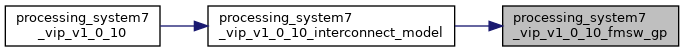

Definition at line 3939 of file processing_system7_vip_v1_0_vl_rfs.sv.

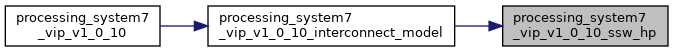

References processing_system7_vip_v1_0_10_arb_rd(), processing_system7_vip_v1_0_10_arb_wr(), processing_system7_vip_v1_0_10_fmsw_gp(), and processing_system7_vip_v1_0_10_ssw_hp().

Referenced by processing_system7_vip_v1_0_10().

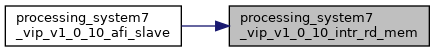

| module processing_system7_vip_v1_0_10_intr_rd_mem | ( | sw_clk | , |

| rstn | , | ||

| full | , | ||

| empty | , | ||

| req | , | ||

| invalid_rd_req | , | ||

| rd_info | , | ||

| RD_DATA_OCM | , | ||

| RD_DATA_DDR | , | ||

| RD_DATA_VALID_OCM | , | ||

| RD_DATA_VALID_DDR | |||

| ) |

Definition at line 3199 of file processing_system7_vip_v1_0_vl_rfs.sv.

Referenced by processing_system7_vip_v1_0_10_afi_slave().

| module processing_system7_vip_v1_0_10_intr_wr_mem | ( | sw_clk | , |

| rstn | , | ||

| full | , | ||

| WR_DATA_ACK_OCM | , | ||

| WR_DATA_ACK_DDR | , | ||

| WR_ADDR | , | ||

| WR_DATA | , | ||

| WR_BYTES | , | ||

| WR_QOS | , | ||

| WR_DATA_VALID_OCM | , | ||

| WR_DATA_VALID_DDR | |||

| ) |

Definition at line 3078 of file processing_system7_vip_v1_0_vl_rfs.sv.

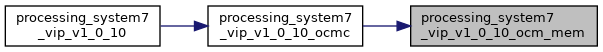

| module processing_system7_vip_v1_0_10_ocm_mem | ( | ) |

256 KB

256 KB memory

256 KB memory

for unaliged address necessary to check for mem_wd-1 , accordingly we have to pad post bytes.

Definition at line 2690 of file processing_system7_vip_v1_0_vl_rfs.sv.

Referenced by processing_system7_vip_v1_0_10_ocmc().

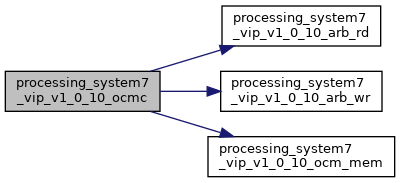

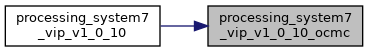

| module processing_system7_vip_v1_0_10_ocmc | ( | rstn | , |

| sw_clk | , | ||

| ocm_wr_ack_port0 | , | ||

| ocm_wr_dv_port0 | , | ||

| ocm_rd_req_port0 | , | ||

| ocm_rd_dv_port0 | , | ||

| ocm_wr_addr_port0 | , | ||

| ocm_wr_data_port0 | , | ||

| ocm_wr_strb_port0 | , | ||

| ocm_wr_bytes_port0 | , | ||

| ocm_rd_addr_port0 | , | ||

| ocm_rd_data_port0 | , | ||

| ocm_rd_bytes_port0 | , | ||

| ocm_wr_qos_port0 | , | ||

| ocm_rd_qos_port0 | , | ||

| ocm_wr_ack_port1 | , | ||

| ocm_wr_dv_port1 | , | ||

| ocm_rd_req_port1 | , | ||

| ocm_rd_dv_port1 | , | ||

| ocm_wr_addr_port1 | , | ||

| ocm_wr_data_port1 | , | ||

| ocm_wr_strb_port1 | , | ||

| ocm_wr_bytes_port1 | , | ||

| ocm_rd_addr_port1 | , | ||

| ocm_rd_data_port1 | , | ||

| ocm_rd_bytes_port1 | , | ||

| ocm_wr_qos_port1 | , | ||

| ocm_rd_qos_port1 | |||

| ) |

if

Definition at line 3736 of file processing_system7_vip_v1_0_vl_rfs.sv.

References processing_system7_vip_v1_0_10_arb_rd(), processing_system7_vip_v1_0_10_arb_wr(), and processing_system7_vip_v1_0_10_ocm_mem().

Referenced by processing_system7_vip_v1_0_10().

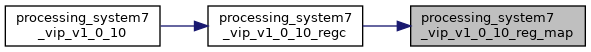

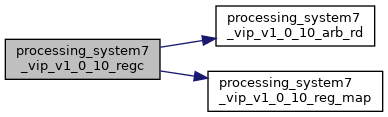

| module processing_system7_vip_v1_0_10_reg_map | ( | ) |

as the memory is implemented 4 byte wide

as the memory is implemented 4 byte wide 256 MB

Definition at line 2540 of file processing_system7_vip_v1_0_vl_rfs.sv.

Referenced by processing_system7_vip_v1_0_10_regc().

| module processing_system7_vip_v1_0_10_regc | ( | rstn | , |

| sw_clk | , | ||

| reg_rd_req_port0 | , | ||

| reg_rd_dv_port0 | , | ||

| reg_rd_addr_port0 | , | ||

| reg_rd_data_port0 | , | ||

| reg_rd_bytes_port0 | , | ||