|

SimpleVOut

1.0.0 Initial

A Simple FPGA Core for Creating VGA/DVI/HDMI/OpenLDI Signals

|

|

SimpleVOut

1.0.0 Initial

A Simple FPGA Core for Creating VGA/DVI/HDMI/OpenLDI Signals

|

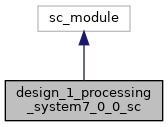

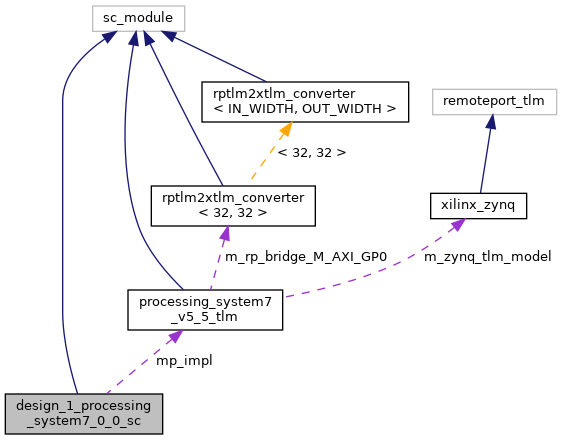

#include <design_1_processing_system7_0_0_sc.h>

Public Member Functions | |

| design_1_processing_system7_0_0_sc (const sc_core::sc_module_name &nm) | |

| virtual | ~design_1_processing_system7_0_0_sc () |

Public Attributes | |

| xtlm::xtlm_aximm_initiator_socket * | M_AXI_GP0_rd_socket |

| xtlm::xtlm_aximm_initiator_socket * | M_AXI_GP0_wr_socket |

| xtlm::xtlm_aximm_target_socket * | S_AXI_HP0_rd_socket |

| xtlm::xtlm_aximm_target_socket * | S_AXI_HP0_wr_socket |

Protected Attributes | |

| processing_system7_v5_5_tlm * | mp_impl |

Private Member Functions | |

| design_1_processing_system7_0_0_sc (const design_1_processing_system7_0_0_sc &) | |

| const design_1_processing_system7_0_0_sc & | operator= (const design_1_processing_system7_0_0_sc &) |

Definition at line 70 of file design_1_processing_system7_0_0_sc.h.

| design_1_processing_system7_0_0_sc::design_1_processing_system7_0_0_sc | ( | const sc_core::sc_module_name & | nm | ) |

Definition at line 57 of file design_1_processing_system7_0_0_sc.cpp.

References M_AXI_GP0_rd_socket, processing_system7_v5_5_tlm::M_AXI_GP0_rd_socket, M_AXI_GP0_wr_socket, processing_system7_v5_5_tlm::M_AXI_GP0_wr_socket, mp_impl, S_AXI_HP0_rd_socket, processing_system7_v5_5_tlm::S_AXI_HP0_rd_socket, S_AXI_HP0_wr_socket, and processing_system7_v5_5_tlm::S_AXI_HP0_wr_socket.

|

virtual |

Definition at line 130 of file design_1_processing_system7_0_0_sc.cpp.

References mp_impl.

|

private |

|

private |

| xtlm::xtlm_aximm_initiator_socket* design_1_processing_system7_0_0_sc::M_AXI_GP0_rd_socket |

Definition at line 79 of file design_1_processing_system7_0_0_sc.h.

Referenced by design_1_processing_system7_0_0_sc().

| xtlm::xtlm_aximm_initiator_socket* design_1_processing_system7_0_0_sc::M_AXI_GP0_wr_socket |

Definition at line 80 of file design_1_processing_system7_0_0_sc.h.

Referenced by design_1_processing_system7_0_0_sc().

|

protected |

Definition at line 89 of file design_1_processing_system7_0_0_sc.h.

Referenced by design_1_processing_system7_0_0_sc(), and ~design_1_processing_system7_0_0_sc().

| xtlm::xtlm_aximm_target_socket* design_1_processing_system7_0_0_sc::S_AXI_HP0_rd_socket |

Definition at line 81 of file design_1_processing_system7_0_0_sc.h.

Referenced by design_1_processing_system7_0_0_sc().

| xtlm::xtlm_aximm_target_socket* design_1_processing_system7_0_0_sc::S_AXI_HP0_wr_socket |

Definition at line 82 of file design_1_processing_system7_0_0_sc.h.

Referenced by design_1_processing_system7_0_0_sc().