|

SimpleVOut

1.0.0 Initial

A Simple FPGA Core for Creating VGA/DVI/HDMI/OpenLDI Signals

|

|

SimpleVOut

1.0.0 Initial

A Simple FPGA Core for Creating VGA/DVI/HDMI/OpenLDI Signals

|

#include <processing_system7_v5_5_tlm.h>

Public Member Functions | |

| processing_system7_v5_5_tlm (sc_core::sc_module_name name, xsc::common_cpp::properties &) | |

| ~processing_system7_v5_5_tlm () | |

| SC_HAS_PROCESS (processing_system7_v5_5_tlm) | |

Public Attributes | |

| sc_core::sc_out< sc_dt::sc_bv< 1 > > | ENET0_GMII_TX_EN |

| sc_core::sc_out< sc_dt::sc_bv< 1 > > | ENET0_GMII_TX_ER |

| sc_core::sc_out< bool > | ENET0_MDIO_MDC |

| sc_core::sc_out< bool > | ENET0_MDIO_O |

| sc_core::sc_out< bool > | ENET0_MDIO_T |

| sc_core::sc_out< sc_dt::sc_bv< 8 > > | ENET0_GMII_TXD |

| sc_core::sc_in< bool > | ENET0_GMII_COL |

| sc_core::sc_in< bool > | ENET0_GMII_CRS |

| sc_core::sc_in< bool > | ENET0_GMII_RX_CLK |

| sc_core::sc_in< bool > | ENET0_GMII_RX_DV |

| sc_core::sc_in< bool > | ENET0_GMII_RX_ER |

| sc_core::sc_in< bool > | ENET0_GMII_TX_CLK |

| sc_core::sc_in< bool > | ENET0_MDIO_I |

| sc_core::sc_in< bool > | ENET0_EXT_INTIN |

| sc_core::sc_in< sc_dt::sc_bv< 8 > > | ENET0_GMII_RXD |

| sc_core::sc_in< sc_dt::sc_bv< 8 > > | GPIO_I |

| sc_core::sc_out< sc_dt::sc_bv< 8 > > | GPIO_O |

| sc_core::sc_out< sc_dt::sc_bv< 8 > > | GPIO_T |

| sc_core::sc_out< bool > | TTC0_WAVE0_OUT |

| sc_core::sc_out< bool > | TTC0_WAVE1_OUT |

| sc_core::sc_out< bool > | TTC0_WAVE2_OUT |

| sc_core::sc_in< bool > | M_AXI_GP0_ACLK |

| sc_core::sc_out< sc_dt::sc_bv< 8 > > | S_AXI_HP0_RCOUNT |

| sc_core::sc_out< sc_dt::sc_bv< 8 > > | S_AXI_HP0_WCOUNT |

| sc_core::sc_out< sc_dt::sc_bv< 3 > > | S_AXI_HP0_RACOUNT |

| sc_core::sc_out< sc_dt::sc_bv< 6 > > | S_AXI_HP0_WACOUNT |

| sc_core::sc_in< bool > | S_AXI_HP0_ACLK |

| sc_core::sc_in< bool > | S_AXI_HP0_RDISSUECAP1_EN |

| sc_core::sc_in< bool > | S_AXI_HP0_WRISSUECAP1_EN |

| sc_core::sc_in< sc_dt::sc_bv< 1 > > | IRQ_F2P |

| sc_core::sc_out< bool > | FCLK_CLK0 |

| sc_core::sc_out< bool > | FCLK_CLK1 |

| sc_core::sc_out< bool > | FCLK_CLK2 |

| sc_core::sc_out< bool > | FCLK_CLK3 |

| sc_core::sc_out< bool > | FCLK_RESET0_N |

| sc_core::sc_inout< sc_dt::sc_bv< 54 > > | MIO |

| sc_core::sc_inout< bool > | DDR_CAS_n |

| sc_core::sc_inout< bool > | DDR_CKE |

| sc_core::sc_inout< bool > | DDR_Clk_n |

| sc_core::sc_inout< bool > | DDR_Clk |

| sc_core::sc_inout< bool > | DDR_CS_n |

| sc_core::sc_inout< bool > | DDR_DRSTB |

| sc_core::sc_inout< bool > | DDR_ODT |

| sc_core::sc_inout< bool > | DDR_RAS_n |

| sc_core::sc_inout< bool > | DDR_WEB |

| sc_core::sc_inout< sc_dt::sc_bv< 3 > > | DDR_BankAddr |

| sc_core::sc_inout< sc_dt::sc_bv< 15 > > | DDR_Addr |

| sc_core::sc_inout< bool > | DDR_VRN |

| sc_core::sc_inout< bool > | DDR_VRP |

| sc_core::sc_inout< sc_dt::sc_bv< 4 > > | DDR_DM |

| sc_core::sc_inout< sc_dt::sc_bv< 32 > > | DDR_DQ |

| sc_core::sc_inout< sc_dt::sc_bv< 4 > > | DDR_DQS_n |

| sc_core::sc_inout< sc_dt::sc_bv< 4 > > | DDR_DQS |

| sc_core::sc_inout< bool > | PS_SRSTB |

| sc_core::sc_inout< bool > | PS_CLK |

| sc_core::sc_inout< bool > | PS_PORB |

| xtlm::xtlm_aximm_initiator_socket * | M_AXI_GP0_wr_socket |

| xtlm::xtlm_aximm_initiator_socket * | M_AXI_GP0_rd_socket |

| xtlm::xtlm_aximm_target_socket * | S_AXI_HP0_wr_socket |

| xtlm::xtlm_aximm_target_socket * | S_AXI_HP0_rd_socket |

Private Member Functions | |

| void | trigger_FCLK_CLK0_pin () |

| void | trigger_FCLK_CLK1_pin () |

| void | trigger_FCLK_CLK2_pin () |

| void | trigger_FCLK_CLK3_pin () |

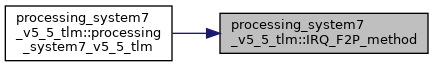

| void | IRQ_F2P_method () |

| void | FCLK_RESET0_N_trigger () |

| void | start_of_simulation () |

Private Attributes | |

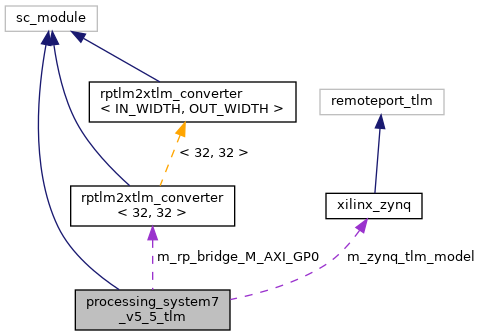

| xilinx_zynq * | m_zynq_tlm_model |

| xtlm::xaximm_xtlm2tlm_t< 64, 32 > | S_AXI_HP0_xtlm_brdg |

| xtlm::xtlm_aximm_fifo * | S_AXI_HP0_buff |

| rptlm2xtlm_converter< 32, 32 > | m_rp_bridge_M_AXI_GP0 |

| sc_core::sc_clock | FCLK_CLK0_clk |

| sc_core::sc_clock | FCLK_CLK1_clk |

| sc_core::sc_clock | FCLK_CLK2_clk |

| sc_core::sc_clock | FCLK_CLK3_clk |

| sc_signal< bool > | qemu_rst |

| xsc::common_cpp::properties | prop |

Definition at line 133 of file processing_system7_v5_5_tlm.h.

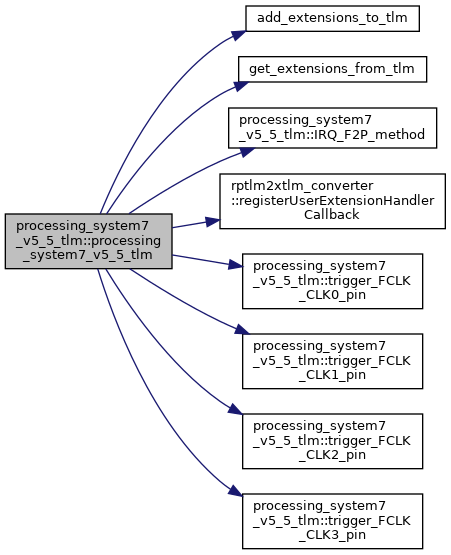

| processing_system7_v5_5_tlm::processing_system7_v5_5_tlm | ( | sc_core::sc_module_name | name, |

| xsc::common_cpp::properties & | _prop | ||

| ) |

Definition at line 145 of file processing_system7_v5_5_tlm.cpp.

References add_extensions_to_tlm(), FCLK_CLK0_clk, FCLK_CLK1_clk, FCLK_CLK2_clk, FCLK_CLK3_clk, get_extensions_from_tlm(), IRQ_F2P, IRQ_F2P_method(), xilinx_zynq::m_axi_gp, M_AXI_GP0_rd_socket, M_AXI_GP0_wr_socket, m_rp_bridge_M_AXI_GP0, m_zynq_tlm_model, qemu_rst, rptlm2xtlm_converter< IN_WIDTH, OUT_WIDTH >::rd_socket, rptlm2xtlm_converter< IN_WIDTH, OUT_WIDTH >::registerUserExtensionHandlerCallback(), xilinx_zynq::s_axi_hp, S_AXI_HP0_buff, S_AXI_HP0_rd_socket, S_AXI_HP0_wr_socket, S_AXI_HP0_xtlm_brdg, rptlm2xtlm_converter< IN_WIDTH, OUT_WIDTH >::target_socket, trigger_FCLK_CLK0_pin(), trigger_FCLK_CLK1_pin(), trigger_FCLK_CLK2_pin(), trigger_FCLK_CLK3_pin(), and rptlm2xtlm_converter< IN_WIDTH, OUT_WIDTH >::wr_socket.

| processing_system7_v5_5_tlm::~processing_system7_v5_5_tlm | ( | ) |

Definition at line 283 of file processing_system7_v5_5_tlm.cpp.

References M_AXI_GP0_rd_socket, M_AXI_GP0_wr_socket, S_AXI_HP0_buff, S_AXI_HP0_rd_socket, and S_AXI_HP0_wr_socket.

|

private |

Definition at line 324 of file processing_system7_v5_5_tlm.cpp.

References FCLK_RESET0_N, m_zynq_tlm_model, and xilinx_zynq::ps2pl_rst.

|

private |

Definition at line 312 of file processing_system7_v5_5_tlm.cpp.

References IRQ_F2P, m_zynq_tlm_model, xilinx_zynq::pl2ps_irq, and prop.

Referenced by processing_system7_v5_5_tlm().

| processing_system7_v5_5_tlm::SC_HAS_PROCESS | ( | processing_system7_v5_5_tlm | ) |

|

private |

Definition at line 327 of file processing_system7_v5_5_tlm.cpp.

References FCLK_RESET0_N, and qemu_rst.

|

private |

Definition at line 294 of file processing_system7_v5_5_tlm.cpp.

References FCLK_CLK0, and FCLK_CLK0_clk.

Referenced by processing_system7_v5_5_tlm().

|

private |

Definition at line 299 of file processing_system7_v5_5_tlm.cpp.

References FCLK_CLK1, and FCLK_CLK1_clk.

Referenced by processing_system7_v5_5_tlm().

|

private |

Definition at line 304 of file processing_system7_v5_5_tlm.cpp.

References FCLK_CLK2, and FCLK_CLK2_clk.

Referenced by processing_system7_v5_5_tlm().

|

private |

Definition at line 309 of file processing_system7_v5_5_tlm.cpp.

References FCLK_CLK3, and FCLK_CLK3_clk.

Referenced by processing_system7_v5_5_tlm().

| sc_core::sc_inout<sc_dt::sc_bv<15> > processing_system7_v5_5_tlm::DDR_Addr |

Definition at line 183 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<sc_dt::sc_bv<3> > processing_system7_v5_5_tlm::DDR_BankAddr |

Definition at line 182 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::DDR_CAS_n |

Definition at line 173 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::DDR_CKE |

Definition at line 174 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::DDR_Clk |

Definition at line 176 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::DDR_Clk_n |

Definition at line 175 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::DDR_CS_n |

Definition at line 177 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<sc_dt::sc_bv<4> > processing_system7_v5_5_tlm::DDR_DM |

Definition at line 186 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<sc_dt::sc_bv<32> > processing_system7_v5_5_tlm::DDR_DQ |

Definition at line 187 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<sc_dt::sc_bv<4> > processing_system7_v5_5_tlm::DDR_DQS |

Definition at line 189 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<sc_dt::sc_bv<4> > processing_system7_v5_5_tlm::DDR_DQS_n |

Definition at line 188 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::DDR_DRSTB |

Definition at line 178 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::DDR_ODT |

Definition at line 179 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::DDR_RAS_n |

Definition at line 180 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::DDR_VRN |

Definition at line 184 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::DDR_VRP |

Definition at line 185 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::DDR_WEB |

Definition at line 181 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_in<bool> processing_system7_v5_5_tlm::ENET0_EXT_INTIN |

Definition at line 150 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_in<bool> processing_system7_v5_5_tlm::ENET0_GMII_COL |

Definition at line 143 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_in<bool> processing_system7_v5_5_tlm::ENET0_GMII_CRS |

Definition at line 144 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_in<bool> processing_system7_v5_5_tlm::ENET0_GMII_RX_CLK |

Definition at line 145 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_in<bool> processing_system7_v5_5_tlm::ENET0_GMII_RX_DV |

Definition at line 146 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_in<bool> processing_system7_v5_5_tlm::ENET0_GMII_RX_ER |

Definition at line 147 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_in<sc_dt::sc_bv<8> > processing_system7_v5_5_tlm::ENET0_GMII_RXD |

Definition at line 151 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_in<bool> processing_system7_v5_5_tlm::ENET0_GMII_TX_CLK |

Definition at line 148 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<sc_dt::sc_bv<1> > processing_system7_v5_5_tlm::ENET0_GMII_TX_EN |

Definition at line 137 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<sc_dt::sc_bv<1> > processing_system7_v5_5_tlm::ENET0_GMII_TX_ER |

Definition at line 138 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<sc_dt::sc_bv<8> > processing_system7_v5_5_tlm::ENET0_GMII_TXD |

Definition at line 142 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_in<bool> processing_system7_v5_5_tlm::ENET0_MDIO_I |

Definition at line 149 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<bool> processing_system7_v5_5_tlm::ENET0_MDIO_MDC |

Definition at line 139 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<bool> processing_system7_v5_5_tlm::ENET0_MDIO_O |

Definition at line 140 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<bool> processing_system7_v5_5_tlm::ENET0_MDIO_T |

Definition at line 141 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<bool> processing_system7_v5_5_tlm::FCLK_CLK0 |

Definition at line 167 of file processing_system7_v5_5_tlm.h.

Referenced by trigger_FCLK_CLK0_pin().

|

private |

Definition at line 235 of file processing_system7_v5_5_tlm.h.

Referenced by processing_system7_v5_5_tlm(), and trigger_FCLK_CLK0_pin().

| sc_core::sc_out<bool> processing_system7_v5_5_tlm::FCLK_CLK1 |

Definition at line 168 of file processing_system7_v5_5_tlm.h.

Referenced by trigger_FCLK_CLK1_pin().

|

private |

Definition at line 236 of file processing_system7_v5_5_tlm.h.

Referenced by processing_system7_v5_5_tlm(), and trigger_FCLK_CLK1_pin().

| sc_core::sc_out<bool> processing_system7_v5_5_tlm::FCLK_CLK2 |

Definition at line 169 of file processing_system7_v5_5_tlm.h.

Referenced by trigger_FCLK_CLK2_pin().

|

private |

Definition at line 237 of file processing_system7_v5_5_tlm.h.

Referenced by processing_system7_v5_5_tlm(), and trigger_FCLK_CLK2_pin().

| sc_core::sc_out<bool> processing_system7_v5_5_tlm::FCLK_CLK3 |

Definition at line 170 of file processing_system7_v5_5_tlm.h.

Referenced by trigger_FCLK_CLK3_pin().

|

private |

Definition at line 238 of file processing_system7_v5_5_tlm.h.

Referenced by processing_system7_v5_5_tlm(), and trigger_FCLK_CLK3_pin().

| sc_core::sc_out<bool> processing_system7_v5_5_tlm::FCLK_RESET0_N |

Definition at line 171 of file processing_system7_v5_5_tlm.h.

Referenced by FCLK_RESET0_N_trigger(), and start_of_simulation().

| sc_core::sc_in<sc_dt::sc_bv<8> > processing_system7_v5_5_tlm::GPIO_I |

Definition at line 152 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<sc_dt::sc_bv<8> > processing_system7_v5_5_tlm::GPIO_O |

Definition at line 153 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<sc_dt::sc_bv<8> > processing_system7_v5_5_tlm::GPIO_T |

Definition at line 154 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_in<sc_dt::sc_bv<1> > processing_system7_v5_5_tlm::IRQ_F2P |

Definition at line 166 of file processing_system7_v5_5_tlm.h.

Referenced by IRQ_F2P_method(), and processing_system7_v5_5_tlm().

| sc_core::sc_in<bool> processing_system7_v5_5_tlm::M_AXI_GP0_ACLK |

Definition at line 158 of file processing_system7_v5_5_tlm.h.

| xtlm::xtlm_aximm_initiator_socket* processing_system7_v5_5_tlm::M_AXI_GP0_rd_socket |

Definition at line 195 of file processing_system7_v5_5_tlm.h.

Referenced by design_1_processing_system7_0_0_sc::design_1_processing_system7_0_0_sc(), processing_system7_v5_5_tlm(), and ~processing_system7_v5_5_tlm().

| xtlm::xtlm_aximm_initiator_socket* processing_system7_v5_5_tlm::M_AXI_GP0_wr_socket |

Definition at line 194 of file processing_system7_v5_5_tlm.h.

Referenced by design_1_processing_system7_0_0_sc::design_1_processing_system7_0_0_sc(), processing_system7_v5_5_tlm(), and ~processing_system7_v5_5_tlm().

|

private |

Definition at line 231 of file processing_system7_v5_5_tlm.h.

Referenced by processing_system7_v5_5_tlm().

|

private |

Definition at line 216 of file processing_system7_v5_5_tlm.h.

Referenced by FCLK_RESET0_N_trigger(), IRQ_F2P_method(), and processing_system7_v5_5_tlm().

| sc_core::sc_inout<sc_dt::sc_bv<54> > processing_system7_v5_5_tlm::MIO |

Definition at line 172 of file processing_system7_v5_5_tlm.h.

|

private |

Definition at line 262 of file processing_system7_v5_5_tlm.h.

Referenced by IRQ_F2P_method().

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::PS_CLK |

Definition at line 191 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::PS_PORB |

Definition at line 192 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_inout<bool> processing_system7_v5_5_tlm::PS_SRSTB |

Definition at line 190 of file processing_system7_v5_5_tlm.h.

|

private |

Definition at line 259 of file processing_system7_v5_5_tlm.h.

Referenced by processing_system7_v5_5_tlm(), and start_of_simulation().

| sc_core::sc_in<bool> processing_system7_v5_5_tlm::S_AXI_HP0_ACLK |

Definition at line 163 of file processing_system7_v5_5_tlm.h.

|

private |

Definition at line 224 of file processing_system7_v5_5_tlm.h.

Referenced by processing_system7_v5_5_tlm(), and ~processing_system7_v5_5_tlm().

| sc_core::sc_out<sc_dt::sc_bv<3> > processing_system7_v5_5_tlm::S_AXI_HP0_RACOUNT |

Definition at line 161 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<sc_dt::sc_bv<8> > processing_system7_v5_5_tlm::S_AXI_HP0_RCOUNT |

Definition at line 159 of file processing_system7_v5_5_tlm.h.

| xtlm::xtlm_aximm_target_socket* processing_system7_v5_5_tlm::S_AXI_HP0_rd_socket |

Definition at line 197 of file processing_system7_v5_5_tlm.h.

Referenced by design_1_processing_system7_0_0_sc::design_1_processing_system7_0_0_sc(), processing_system7_v5_5_tlm(), and ~processing_system7_v5_5_tlm().

| sc_core::sc_in<bool> processing_system7_v5_5_tlm::S_AXI_HP0_RDISSUECAP1_EN |

Definition at line 164 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<sc_dt::sc_bv<6> > processing_system7_v5_5_tlm::S_AXI_HP0_WACOUNT |

Definition at line 162 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<sc_dt::sc_bv<8> > processing_system7_v5_5_tlm::S_AXI_HP0_WCOUNT |

Definition at line 160 of file processing_system7_v5_5_tlm.h.

| xtlm::xtlm_aximm_target_socket* processing_system7_v5_5_tlm::S_AXI_HP0_wr_socket |

Definition at line 196 of file processing_system7_v5_5_tlm.h.

Referenced by design_1_processing_system7_0_0_sc::design_1_processing_system7_0_0_sc(), processing_system7_v5_5_tlm(), and ~processing_system7_v5_5_tlm().

| sc_core::sc_in<bool> processing_system7_v5_5_tlm::S_AXI_HP0_WRISSUECAP1_EN |

Definition at line 165 of file processing_system7_v5_5_tlm.h.

|

private |

Definition at line 223 of file processing_system7_v5_5_tlm.h.

Referenced by processing_system7_v5_5_tlm().

| sc_core::sc_out<bool> processing_system7_v5_5_tlm::TTC0_WAVE0_OUT |

Definition at line 155 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<bool> processing_system7_v5_5_tlm::TTC0_WAVE1_OUT |

Definition at line 156 of file processing_system7_v5_5_tlm.h.

| sc_core::sc_out<bool> processing_system7_v5_5_tlm::TTC0_WAVE2_OUT |

Definition at line 157 of file processing_system7_v5_5_tlm.h.